# IEEE Standard for High-Speed Test Access Port and On-Chip Distribution Architecture

**IEEE Computer Society**

Sponsored by the Test Technology Standards Committee

# IEEE Standard for High-Speed Test Access Port and On-Chip Distribution Architecture

Sponsor

Test Technology Standards Committee of the IEEE Computer Society

Approved 18 May 2017

**IEEE-SA Standards Board**

**Abstract:** Circuitry that may be built into an integrated circuit to assist in the test, maintenance, and support of assembled printed circuit boards, assembled multi-die packages, and the test of die internal circuits is defined in this standard. The circuitry includes a high-speed TAP (HSTAP) with a packet encoder/decoder and distribution architecture through which instructions and test data are communicated. The standard leverages the languages of IEEE Std 1149.1™ to describe and operate the on-chip circuits.

**Keywords:** 3D-IC, Boundary-Scan Description Language, BSDL, debug, High Speed JTAG, I2C, IEEE 1149.1™, PDL, IEEE 1149.10™, integrated circuit, JTAG, wafer, Procedural Description Language, SERDES, SPI, system level test

Copyright © 2017 by The Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Published 28 July 2017. Printed in the United States of America.

IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by The Institute of Electrical and Electronics Engineers, Incorporated.

PDF: ISBN 978-1-5044-3995-4 STD22564 Print: ISBN 978-1-5044-3996-1 STDPD22564

IEEE prohibits discrimination, harassment, and bullying.

For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA

#### Important Notices and Disclaimers Concerning IEEE Standards Documents

IEEE documents are made available for use subject to important notices and legal disclaimers. These notices and disclaimers, or a reference to this page, appear in all standards and may be found under the heading "Important Notices and Disclaimers Concerning IEEE Standards Documents." They can also be obtained on request from IEEE or viewed at <a href="http://standards.ieee.org/IPR/disclaimers.html">http://standards.ieee.org/IPR/disclaimers.html</a>.

# Notice and Disclaimer of Liability Concerning the Use of IEEE Standards Documents

IEEE Standards documents (standards, recommended practices, and guides), both full-use and trial-use, are developed within IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association ("IEEE-SA") Standards Board. IEEE ("the Institute") develops its standards through a consensus development process, approved by the American National Standards Institute ("ANSI"), which brings together volunteers representing varied viewpoints and interests to achieve the final product. IEEE Standards are documents developed through scientific, academic, and industry-based technical working groups. Volunteers in IEEE working groups are not necessarily members of the Institute and participate without compensation from IEEE. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information or the soundness of any judgments contained in its standards.

IEEE Standards do not guarantee or ensure safety, security, health, or environmental protection, or ensure against interference with or from other devices or networks. Implementers and users of IEEE Standards documents are responsible for determining and complying with all appropriate safety, security, environmental, health, and interference protection practices and all applicable laws and regulations.

IEEE does not warrant or represent the accuracy or content of the material contained in its standards, and expressly disclaims all warranties (express, implied and statutory) not included in this or any other document relating to the standard, including, but not limited to, the warranties of: merchantability; fitness for a particular purpose; non-infringement; and quality, accuracy, effectiveness, currency, or completeness of material. In addition, IEEE disclaims any and all conditions relating to: results; and workmanlike effort. IEEE standards documents are supplied "AS IS" and "WITH ALL FAULTS."

Use of an IEEE standard is wholly voluntary. The existence of an IEEE standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard.

In publishing and making its standards available, IEEE is not suggesting or rendering professional or other services for, or on behalf of, any person or entity nor is IEEE undertaking to perform any duty owed by any other person or entity to another. Any person utilizing any IEEE Standards document, should rely upon his or her own independent judgment in the exercise of reasonable care in any given circumstances or, as appropriate, seek the advice of a competent professional in determining the appropriateness of a given IEEE standard.

IN NO EVENT SHALL IEEE BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO: PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE PUBLICATION, USE OF, OR RELIANCE UPON ANY STANDARD, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE AND REGARDLESS OF WHETHER SUCH DAMAGE WAS FORESEEABLE.

#### **Translations**

The IEEE consensus development process involves the review of documents in English only. In the event that an IEEE standard is translated, only the English version published by IEEE should be considered the approved IEEE standard.

#### Official statements

A statement, written or oral, that is not processed in accordance with the IEEE-SA Standards Board Operations Manual shall not be considered or inferred to be the official position of IEEE or any of its committees and shall not be considered to be, or be relied upon as, a formal position of IEEE. At lectures, symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall make it clear that his or her views should be considered the personal views of that individual rather than the formal position of IEEE.

#### Comments on standards

Comments for revision of IEEE Standards documents are welcome from any interested party, regardless of membership affiliation with IEEE. However, IEEE does not provide consulting information or advice pertaining to IEEE Standards documents. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Since IEEE standards represent a consensus of concerned interests, it is important that any responses to comments and questions also receive the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to comments or questions except in those cases where the matter has previously been addressed. For the same reason, IEEE does not respond to interpretation requests. Any person who would like to participate in revisions to an IEEE standard is welcome to join the relevant IEEE working group.

Comments on standards should be submitted to the following address:

Secretary, IEEE-SA Standards Board 445 Hoes Lane Piscataway, NJ 08854 USA

#### Laws and regulations

Users of IEEE Standards documents should consult all applicable laws and regulations. Compliance with the provisions of any IEEE Standards document does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

#### Copyrights

IEEE draft and approved standards are copyrighted by IEEE under U.S. and international copyright laws. They are made available by IEEE and are adopted for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making these documents available for use and adoption by public authorities and private users, IEEE does not waive any rights in copyright to the documents.

#### **Photocopies**

Subject to payment of the appropriate fee, IEEE will grant users a limited, non-exclusive license to photocopy portions of any individual standard for company or organizational internal use or individual, non-commercial use only. To arrange for payment of licensing fees, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

#### Updating of IEEE Standards documents

Users of IEEE Standards documents should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect.

Every IEEE standard is subjected to review at least every ten years. When a document is more than ten years old and has not undergone a revision process, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE standard.

In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit the IEEE Xplore at <a href="http://ieeexplore.ieee.org/">http://ieeexplore.ieee.org/</a> or contact IEEE at the address listed previously. For more information about the IEEE-SA or IEEE's standards development process, visit the IEEE-SA Website at <a href="http://standards.ieee.org">http://standards.ieee.org</a>.

#### **Errata**

Errata, if any, for all IEEE standards can be accessed on the IEEE-SA Website at the following URL: <a href="http://standards.ieee.org/findstds/errata/index.html">http://standards.ieee.org/findstds/errata/index.html</a>. Users are encouraged to check this URL for errata periodically.

#### **Patents**

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken by the IEEE with respect to the existence or validity of any patent rights in connection therewith. If a patent holder or patent applicant has filed a statement of assurance via an Accepted Letter of Assurance, then the statement is listed on the IEEE-SA Website at <a href="http://standards.ieee.org/about/sasb/patcom/patents.html">http://standards.ieee.org/about/sasb/patcom/patents.html</a>. Letters of Assurance may indicate whether the Submitter is willing or unwilling to grant licenses under patent rights without compensation or under reasonable rates, with reasonable terms and conditions that are demonstrably free of any unfair discrimination to applicants desiring to obtain such licenses.

Essential Patent Claims may exist for which a Letter of Assurance has not been received. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims, or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

#### **Participants**

At the time this IEEE standard was completed, the P1149.10 Working Group had the following membership:

C. J. Clark, Chair and Editor Bill Tuthill, Secretary

Gobinathan AthimolomBob GottliebMike RicchettiTapan ChakrabortyGurgen HarutyunyanCraig StephanJonathon E. ColburnMarc HutnerStephen SunterHeiko EhrenbergDharma KondaBrian TurmelleJosh FerryAdam W. Ley

The following members of the individual balloting committee voted on this standard. Balloters may have voted for approval, disapproval, or abstention.

Saman Adham Heiko Ehrenberg Adam W. Ley Gobinathan Athimolom Jeffrey Moore William Eklow Bill Brown Josh Ferry Charles Ngethe William Bush Jim O'Reilly Joel Goergen **Bob Gottlieb** Juan Carreon Mike Ricchetti Randall Groves Tapan Chakraborty Craig Stephan Peter Harrod Walter Struppler Keith Chow C. J. Clark Gurgen Harutyunyan Stephen Sunter Jonathon E. Colburn Werner Hoelzl David Thompson Glenn Colon-Bonet Marc Hutner Bill Tuthill Adam Cron Piotr Karocki Louis Ungar Jason Doege Dharma Konda Oren Yuen Philippe Lebourg

When the IEEE-SA Standards Board approved this standard on 18 May 2017, it had the following membership:

Jean-Philippe Faure, Chair Gary Hoffman, Vice Chair John D. Kulick, Past Chair Konstantinos Karachalios, Secretary

Chuck Adams Thomas Koshy Robby Robson Dorothy Stanley Masayuki Ariyoshi Joseph L. Koepfinger\* Adrian Stephens Ted Burse Kevin Lu Stephen Dukes Daleep Mohla Mehmet Ulema Doug Edwards Damir Novosel Phil Wennblom J. Travis Griffith Ronald C. Petersen Howard Wolfman Annette D. Reilly Michael Janezic Yu Yuan

<sup>\*</sup>Member Emeritus

#### Introduction

This introduction is not part of IEEE Std 1149.10™-2017, IEEE Standard for High-Speed Test Access Port and On-Chip Distribution Architecture.

With the approval of IEEE Std 1149.1<sup>TM</sup>-2013, the industry now has a standardized approach to hierarchical design-for-test. IEEE Std 1149.1-2013 provides access to IP blocks via IEEE 1500 wrapper serial ports. IEEE 1149.1 package files and PDL standardized how to describe IP block operation destined for SoC integration. Some Working Group members started to discuss the bandwidth limitations of the IEEE 1149.1 TAP, the limitations of single scan-in/scan-out for test time, the diminishing single-ended I/O count for parallel scan due to die-stacking, and the desire for leveraging PDL to be re-used beyond the TAP. A group of interested parties was formed in August of 2013. C. J. Clark presented the fundamentals on the HSTAP, PEDDA, and Packet format at the first meeting. Industry-based SERDES packets were discarded because they required storing packet information in memory and generally required more on-chip resources. The IEEE 1149.10 architecture needed to be simple and easy to add on to the mission mode design. A PAR was approved in October 2013. A publicly available history of the Working Group's attendance, motions, minutes, and presentations can be found at <a href="http://grouper.ieee.org/groups/1149/10/">http://grouper.ieee.org/groups/1149/10/</a>.

#### Contents

| 1. Overview                                                |    |

|------------------------------------------------------------|----|

| 1.1 Scope                                                  |    |

| 1.2 Need                                                   |    |

| 1.3 Document outline                                       |    |

| 1.4 Specifications                                         |    |

| 1.5 Descriptions                                           |    |

| 1.6 Text conventions                                       |    |

| 1.7 Logic diagram conventions                              |    |

| 2. Normative references                                    |    |

| 3. Definitions, abbreviations, acronyms, and special terms | 14 |

| 3.1 Definitions                                            |    |

| 3.2 Abbreviations and acronyms                             |    |

| 3.3 Numbers                                                |    |

| 4. High-speed test access port (HSTAP)                     |    |

| 4.1 HSTAP                                                  |    |

| 5. Packet encoder/decoder and distribution architecture    |    |

| 5.1 PEDDA                                                  |    |

| 6. Packet definitions                                      | 27 |

| 6.1 Packet overview                                        |    |

| 6.2 The CONFIG packet                                      |    |

| 6.3 The TARGET packet                                      |    |

| 6.4 The RESET packet                                       |    |

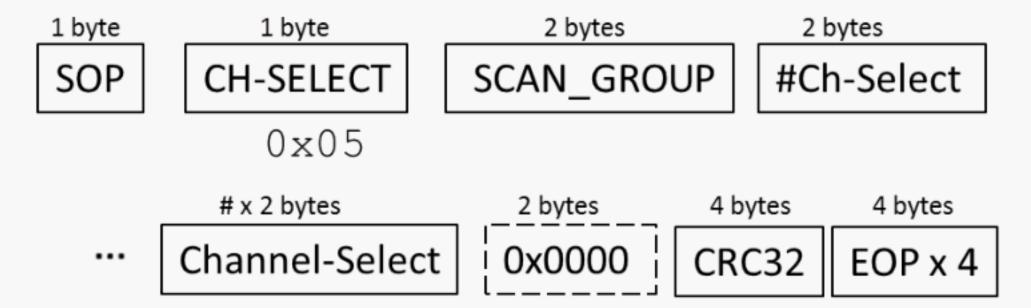

| 6.5 The RAW packet                                         |    |

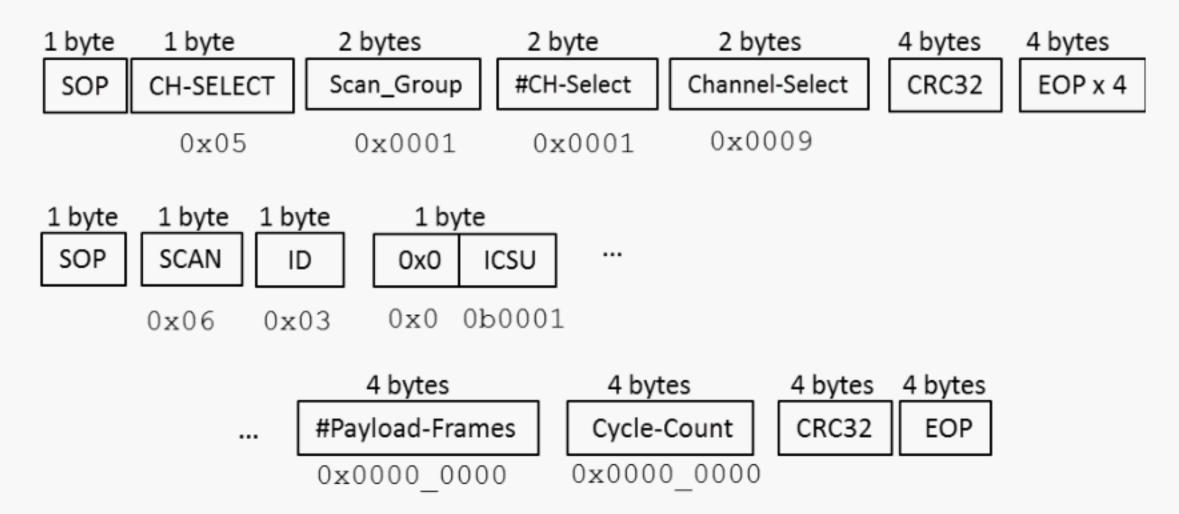

| 6.6 The CH-SELECT packet                                   |    |

| 6.7 The SCAN packet                                        |    |

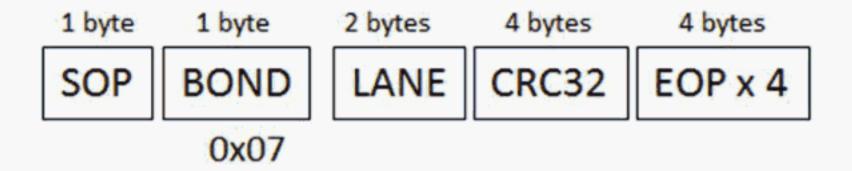

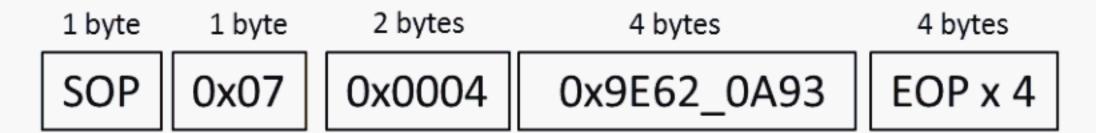

| 6.8 The BOND packet                                        |    |

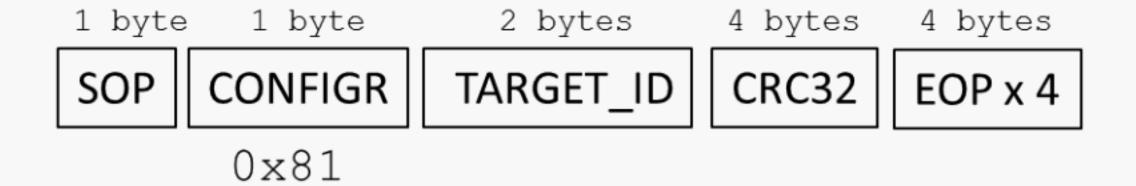

| 6.9 The CONFIGR packet                                     | 47 |

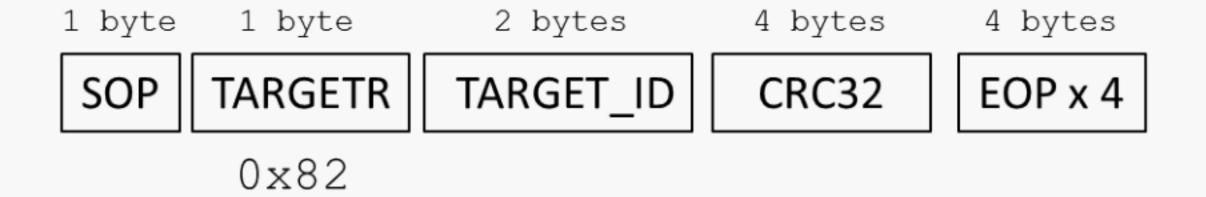

| 6.10 The TARGETR packet                                    | 48 |

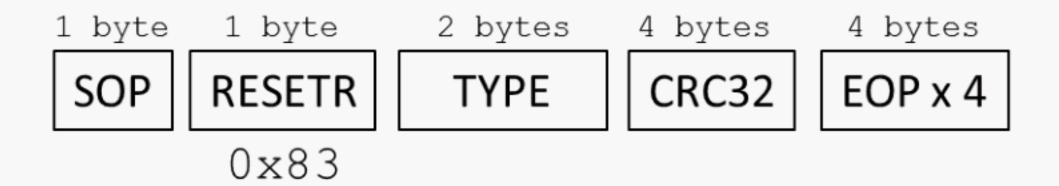

| 6.11 The RESETR packet                                     |    |

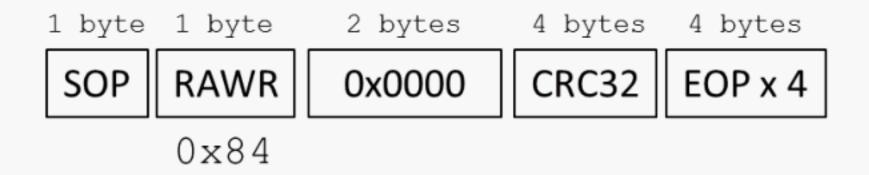

| 6.12 The RAWR packet                                       |    |

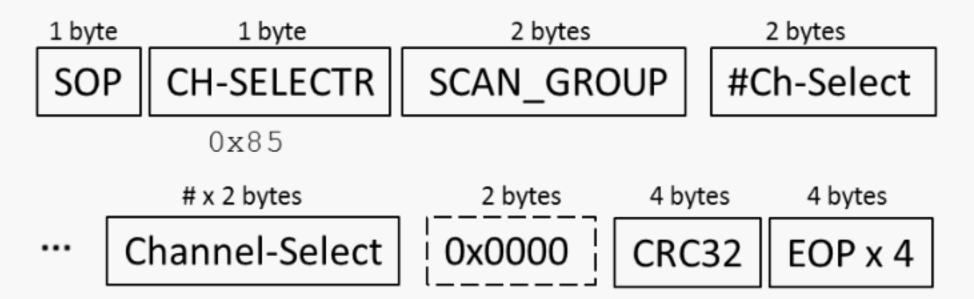

| 6.13 The CH-SELECTR packet                                 |    |

| 6.14 The SCANR packet                                      | 52 |

| 6.15 The BONDR packet                                      |    |

| 7. BSDL definitions                                        | 57 |

| 7.1 BSDL overview                                          | 57 |

| 7.2 Conformance attribute                                  |    |

| 7.3 HSTAP attribute                                        | 59 |

| 7.4 Packet_Map attribute                                   | 67 |

| 7.5 Control_Chars attribute                                | 71 |

| 7.6 Scan_Channel_Association attribute                     |    |

| 7.7 BSDL package for high speed JTAG                       | 76 |

| 8. Channel bonding                                         | 77 |

| 8.1 Optimizing bandwidth                                   |    |

| 9. PDL                                                                                       | 82 |

|----------------------------------------------------------------------------------------------|----|

| 9.1 PDL Overview                                                                             | 82 |

| 9. PDL                                                                                       | 83 |

| 9.3 iTarget command                                                                          | 84 |

| 9.3 iTarget command                                                                          | 85 |

| 9.5 iRaw command                                                                             | 86 |

| 9.6 iBond command                                                                            | 87 |

| 9.7 Standardized PDL procedures                                                              |    |

|                                                                                              |    |

| 10. Compliance verification                                                                  | 89 |

| 10.1 Överview                                                                                | 89 |

|                                                                                              |    |

| Annex A (informative) Bibliography                                                           | 94 |

|                                                                                              |    |

|                                                                                              |    |

|                                                                                              |    |

| List of Figures                                                                              |    |

|                                                                                              |    |

| Figure 1—Logic symbology used in this standard                                               | 14 |

| Figure 2—State diagram for IEEE 1149.10 entry                                                |    |

| Figure 3—Example daisy chain of HSTAPs                                                       |    |

| Figure 4—System that benefits from the compliance-enable character                           |    |

| Figure 5—Example IEEE 1149.10 PEDDA block diagram                                            |    |

| Figure 6—Example implementation of TRST10* and Reset10*                                      |    |

| Figure 7—Example IEEE 1149.1 TDR for asserting Enable_1149_10                                |    |

| Figure 8—Example circuit for asserting Enable_1149_10 via a compliance-enable character      |    |

| Figure 9—Example use of B-S and Init-Data Register                                           |    |

| Figure 10—General form of a IEEE 1149.10 packet                                              |    |

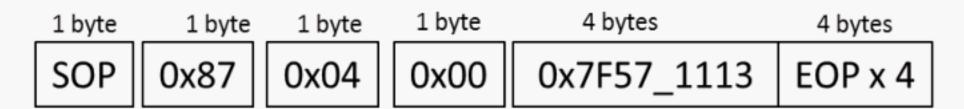

| Figure 11—Format of CONFIG packet                                                            |    |

| Figure 12—Transmit order for CONFIG packet using LSB_First based HSTAP                       |    |

| Figure 13—Format of TARGET packet                                                            |    |

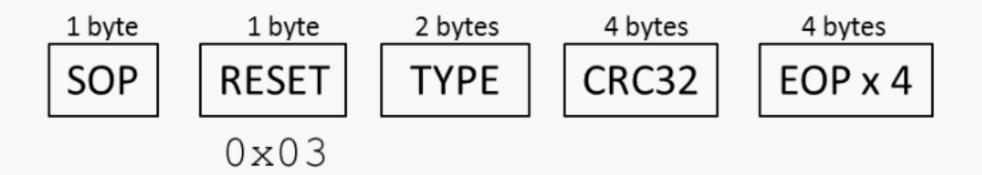

| Figure 14—Format of a RESET packet.                                                          |    |

| Figure 15—Bit transmit order for LSB_First based HSTAP                                       |    |

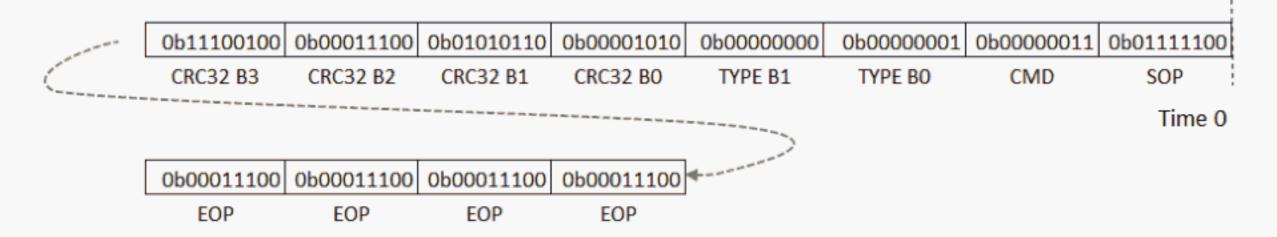

| Figure 16—Format of a RAW packet                                                             |    |

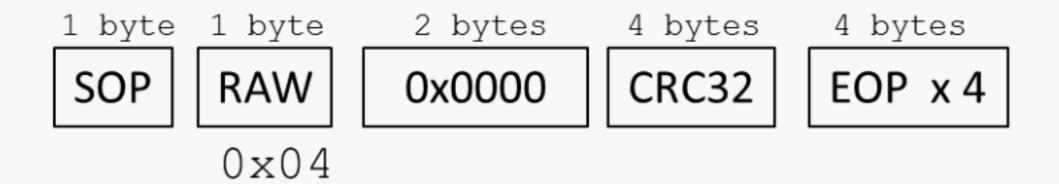

| Figure 17—CH-SELECT packet format                                                            |    |

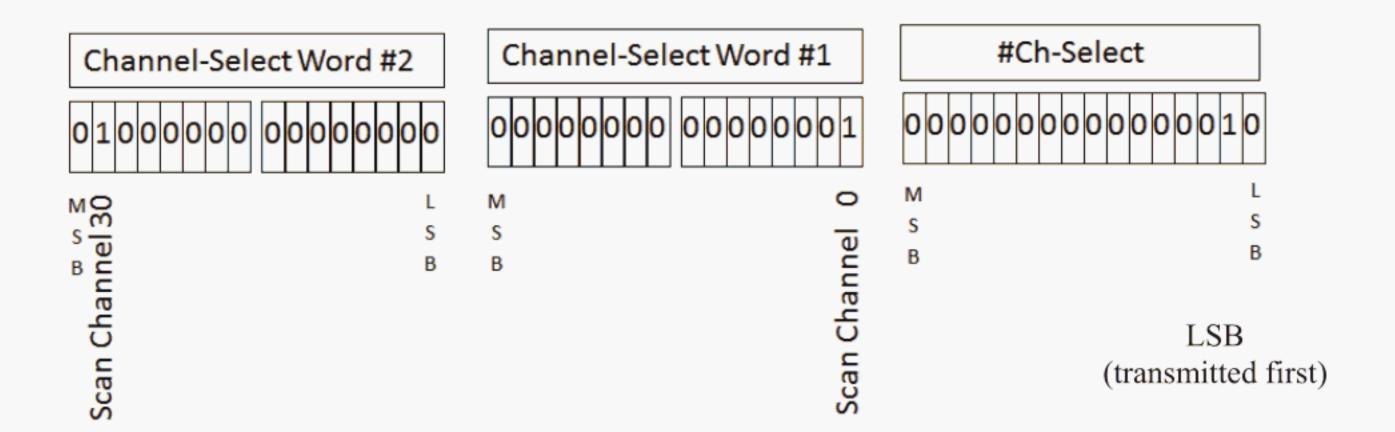

| Figure 18—Example scan-channel selection detail.                                             |    |

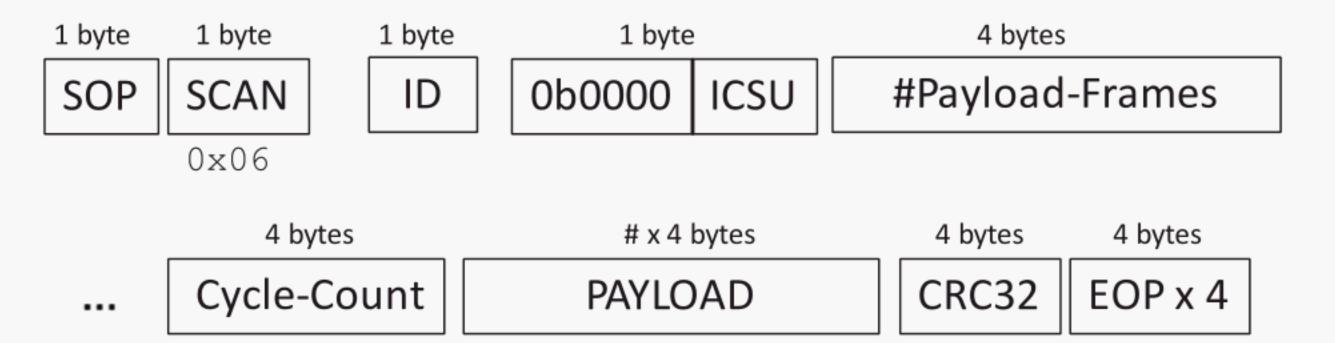

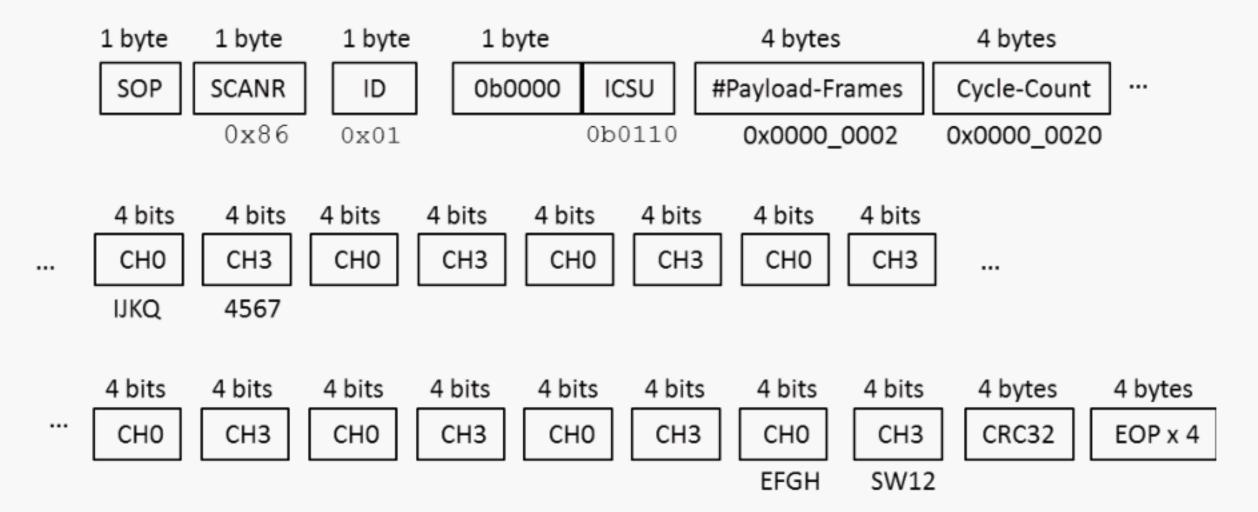

| Figure 19—Generic format of a SCAN packet                                                    |    |

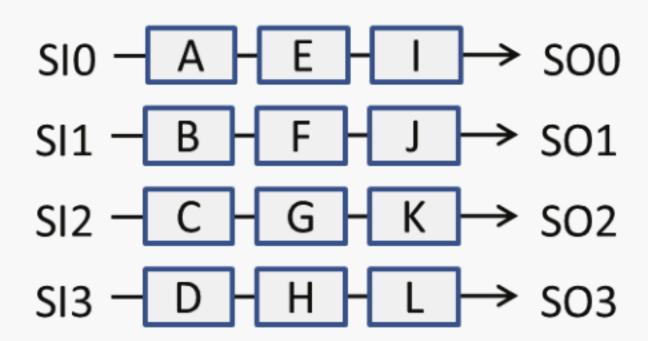

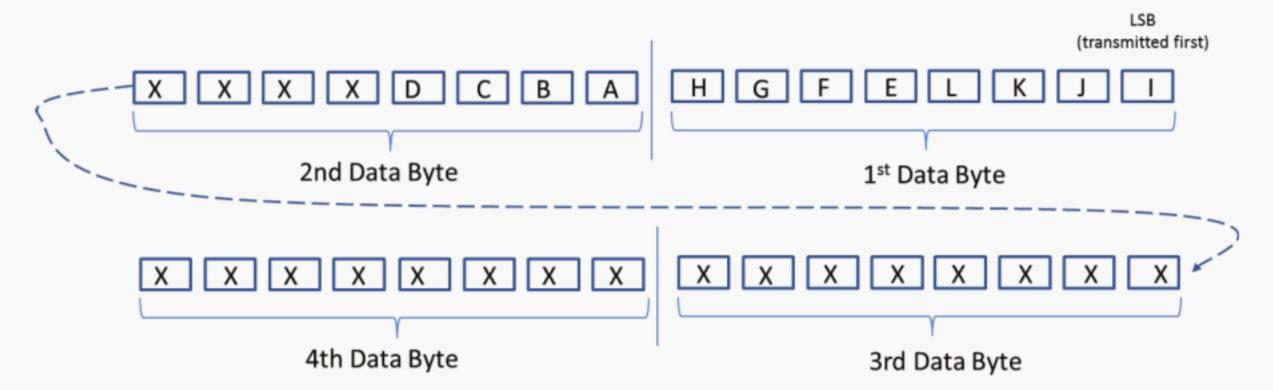

| Figure 20—Data in scan-channel 3 through 6 after scan  Figure 21—Formatted payload of packet |    |

| Figure 22—Payload with 3 scan-channels                                                       |    |

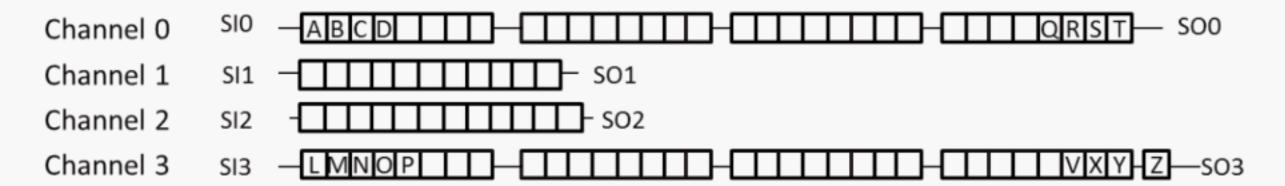

| Figure 23—Four example scan-channels, with final data contents                               |    |

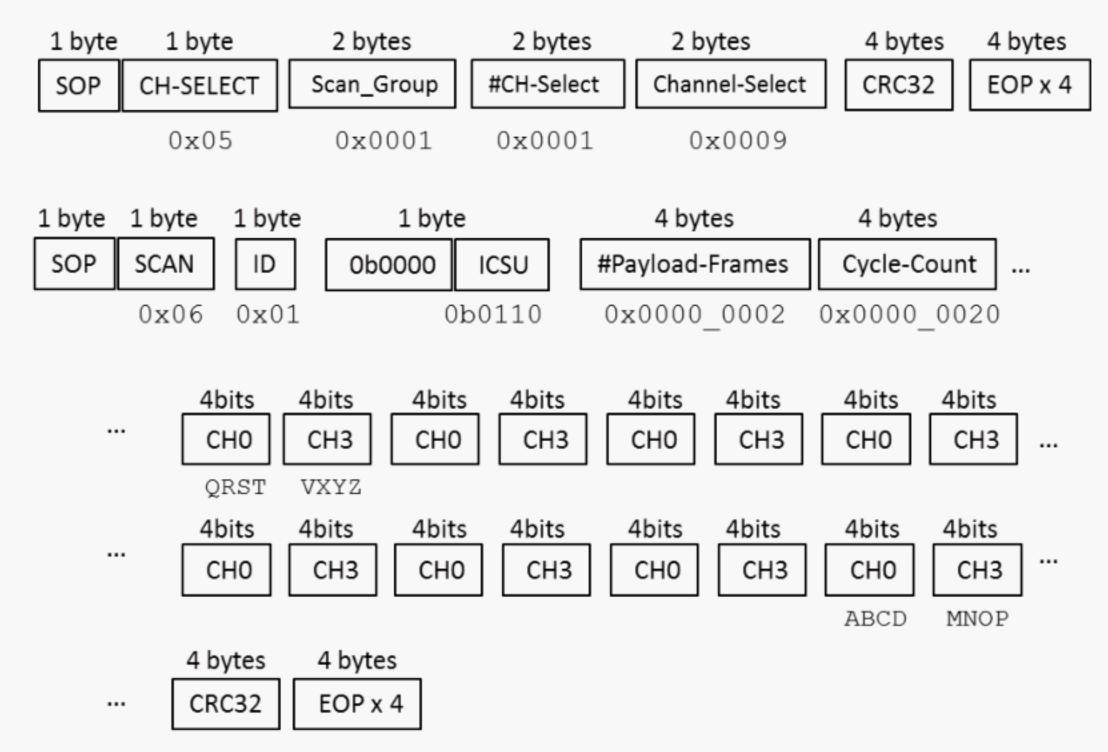

| Figure 24—CH-SELECT, Capture-DR, and Shift-DR portion of a two channel 32-bit scan           |    |

| Figure 25—Example Packet Map                                                                 |    |

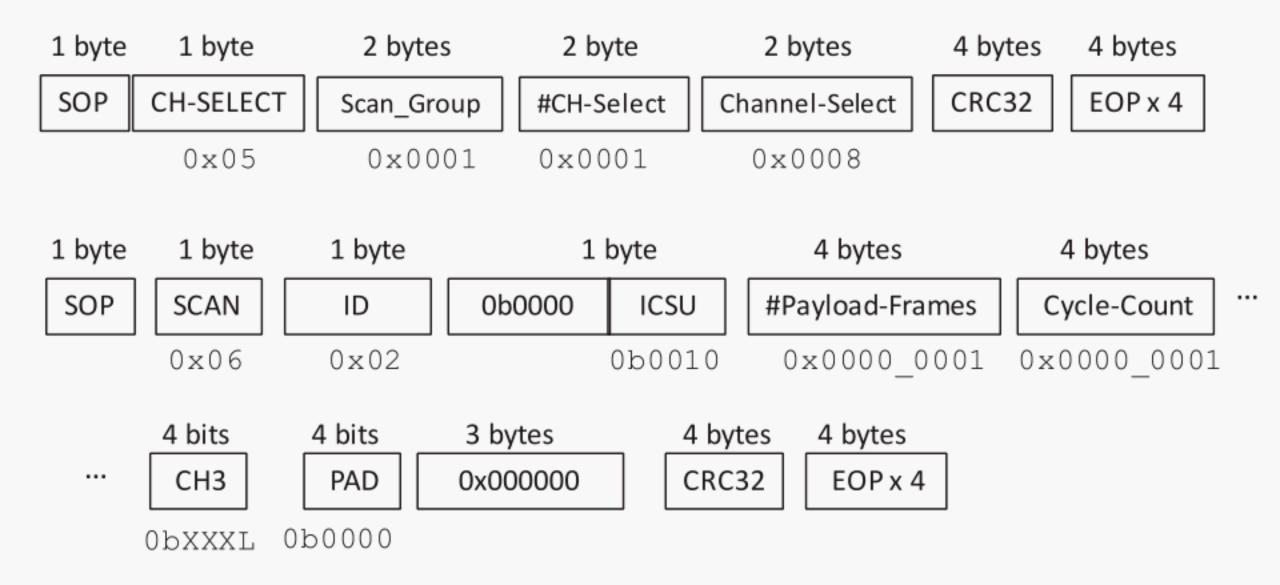

| Figure 26—Packets needed to shift 33rd bit of Channel 3                                      |    |

| Figure 27—Final SCAN packet to assert Update-DR                                              |    |

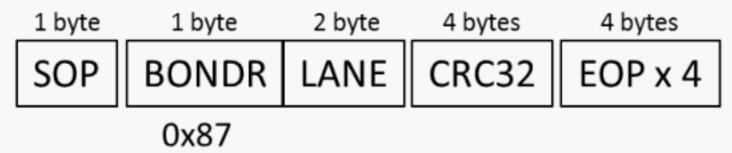

| Figure 28—Format of a BOND packet                                                            |    |

| Figure 29—Example BOND packet for four lanes                                                 |    |

| Figure 30—Format of the CONFIGR packet                                                       |    |

| Figure 31—Format of TARGETR packet                                                           |    |

| Figure 32—Format of the RESETR packet                                                        |    |

| Figure 33—Format of RAWR packet                                                              |    |

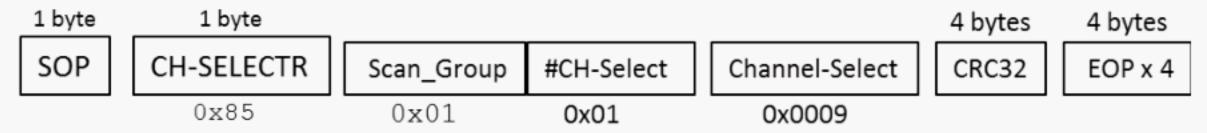

| Figure 34—Format of CH-SELECTR packet                                                        |    |

| Figure 35—CH-SELECTR Packet example                                                          |    |

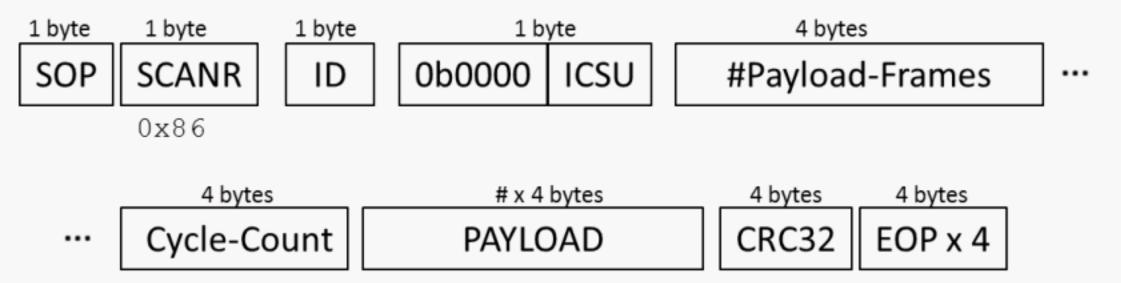

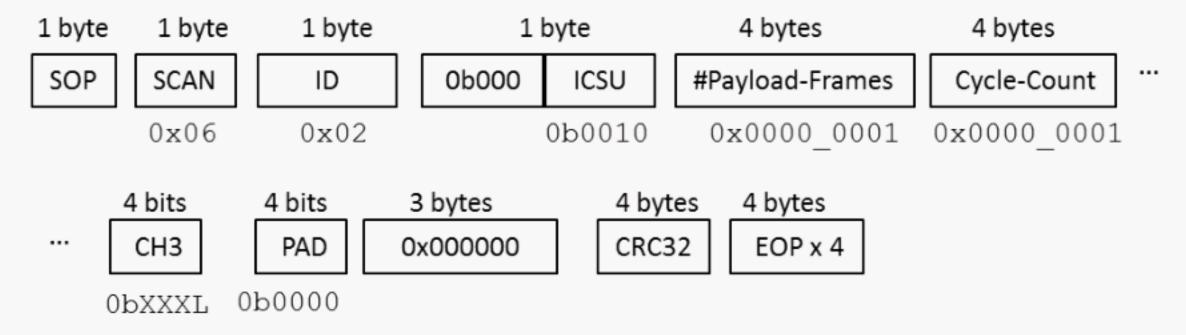

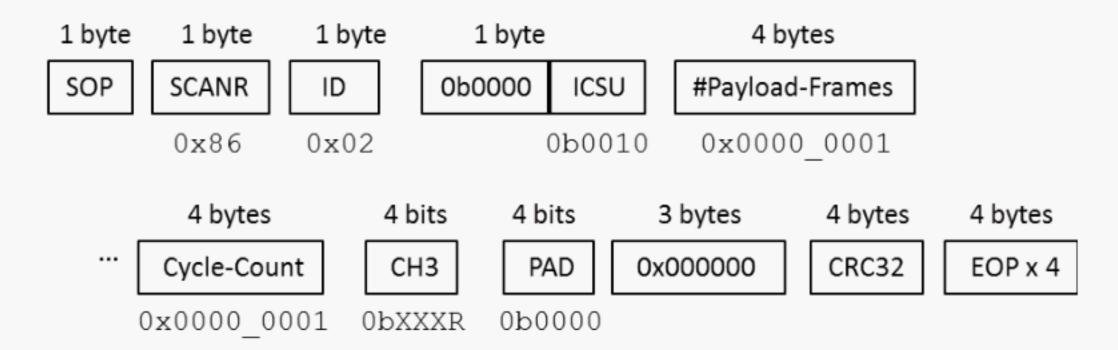

| Figure 36—Generic SCANR packet format                                                        |    |

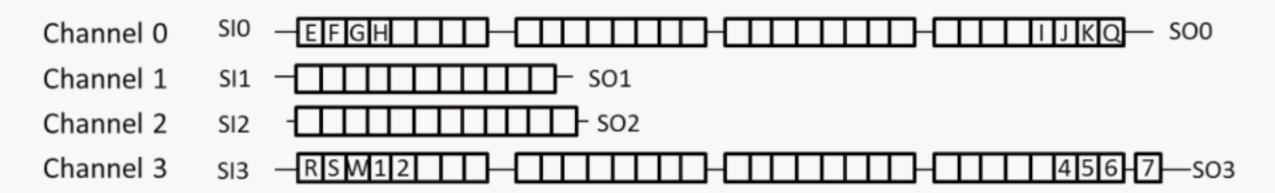

| Figure 37—Four example scan-channels with data captured                                      |    |

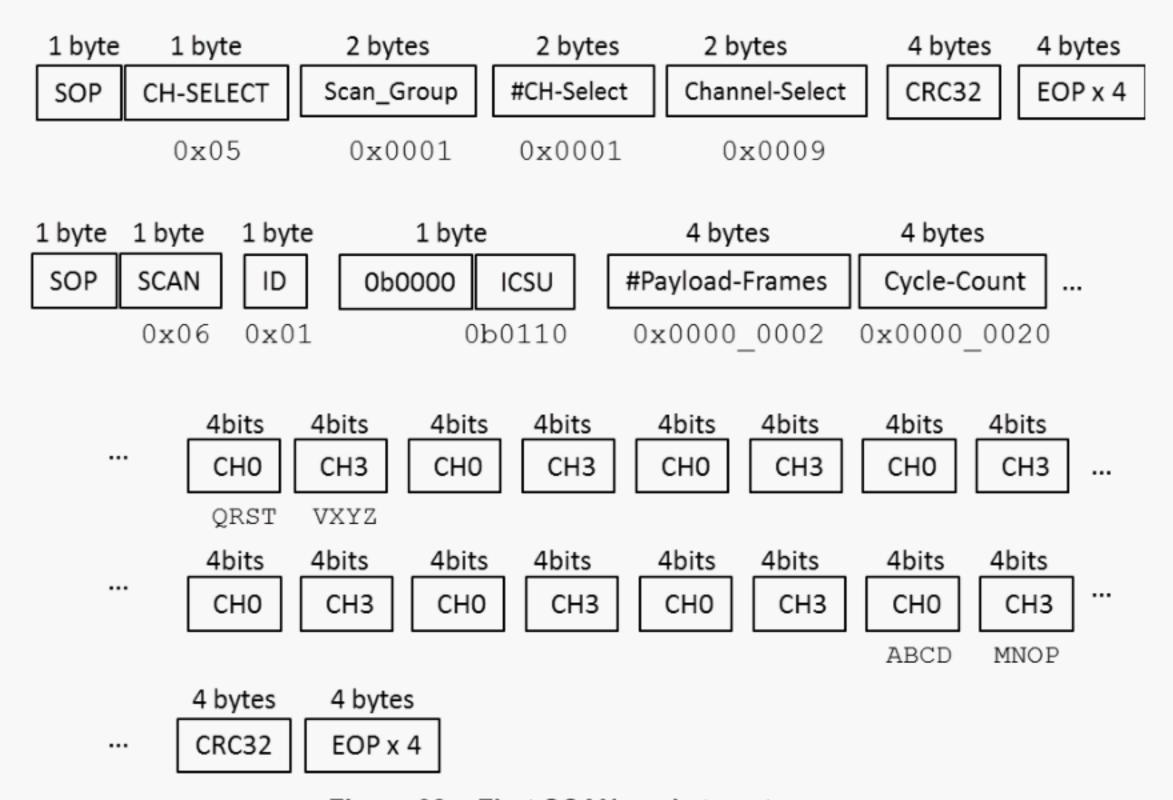

| Figure 38—First SCAN packet sent                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 54                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Figure 39—SCANR response packet example                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 55                                                                         |

| Figure 40—Example SCAN packet for Channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 55                                                                         |

| Figure 41—SCANR response to return last bit of channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 56                                                                         |

| Figure 42—Format of BONDR packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 56                                                                         |

| Figure 43—BONDR response packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                              |

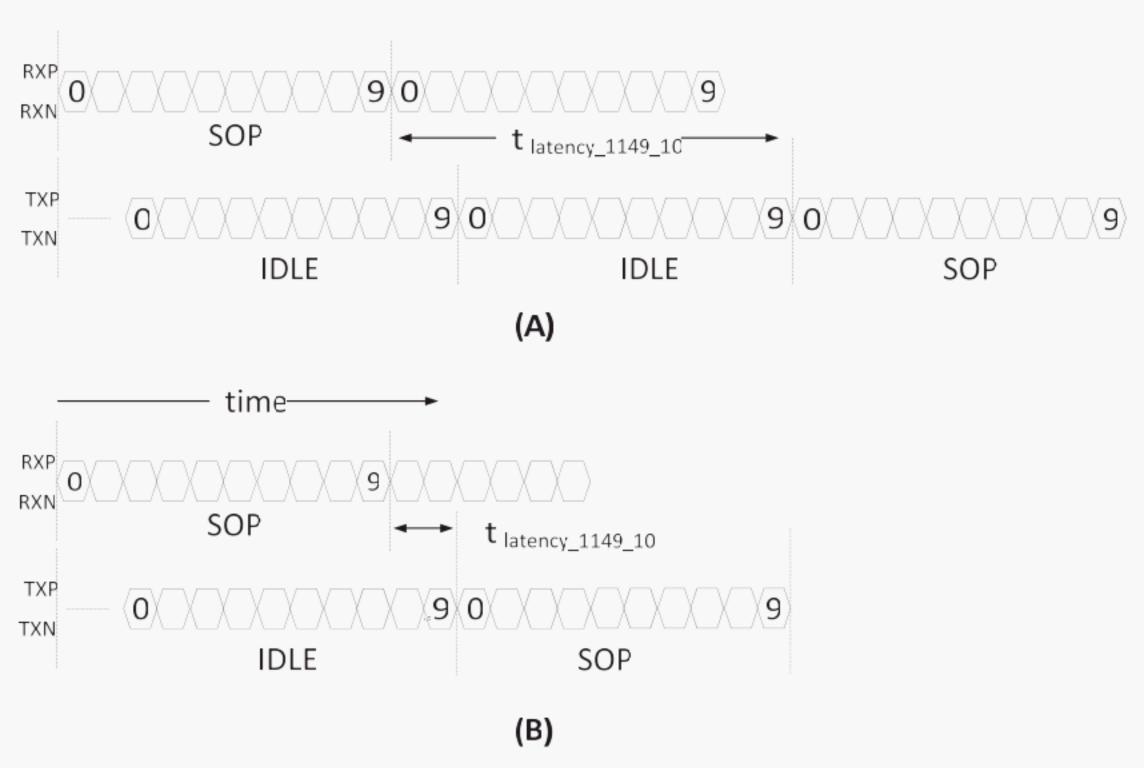

| Figure 44—Example timing for LATENCY 1149 10                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                              |

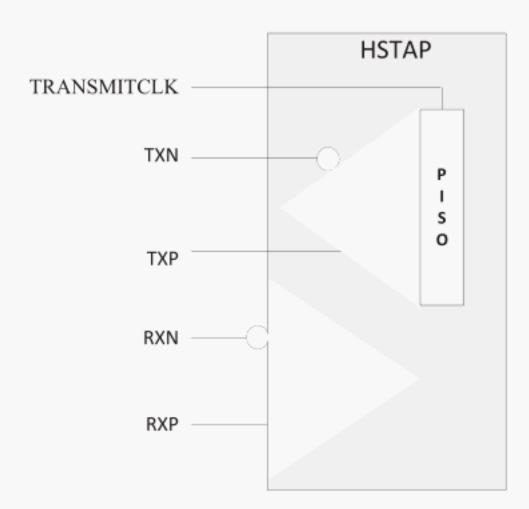

| Figure 45—HSTAP SERDES requiring TX_CLOCK_1149_10 input                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 66                                                                         |

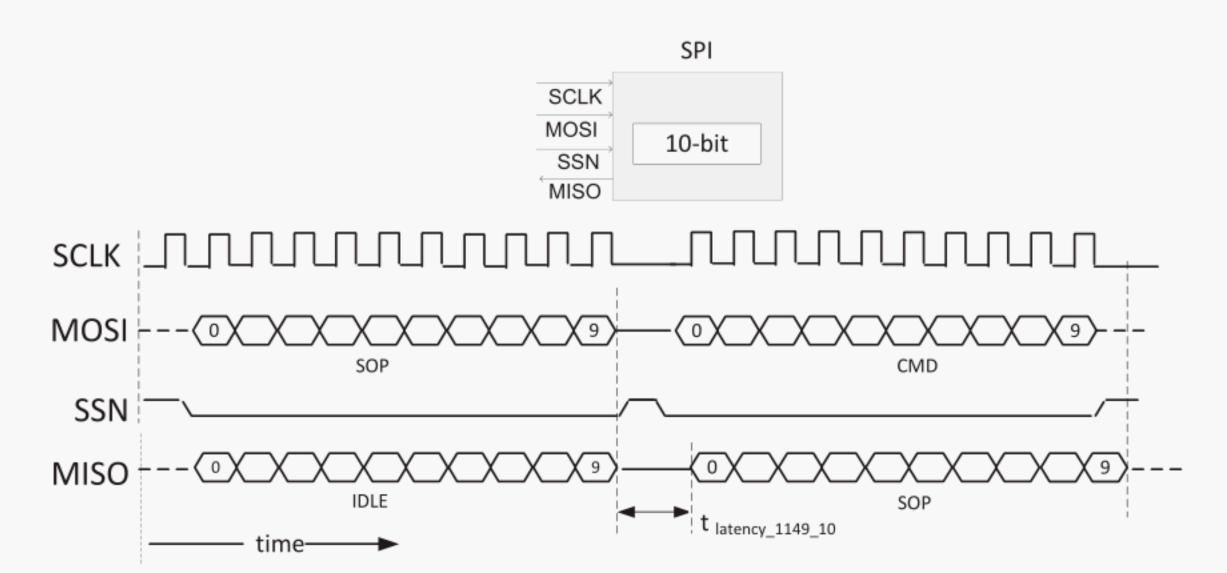

| Figure 46—SPI Bus as HSTAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 67                                                                         |

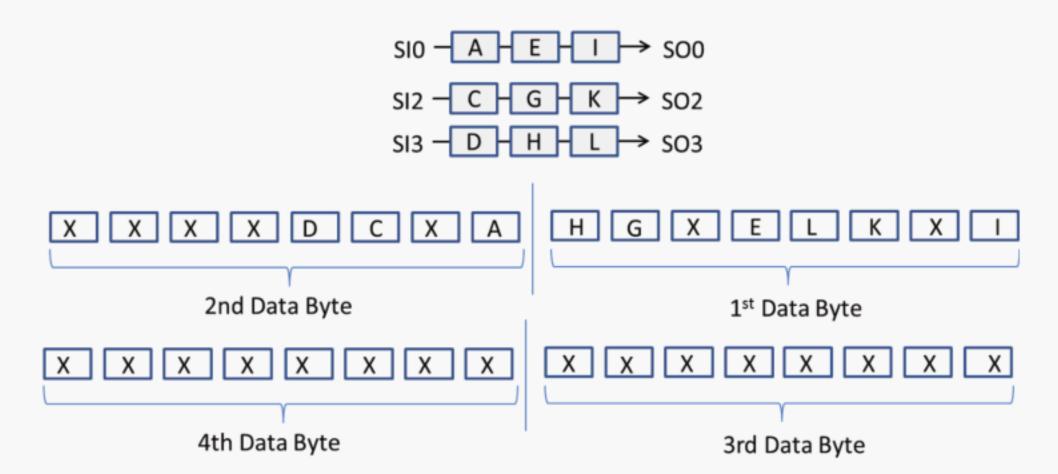

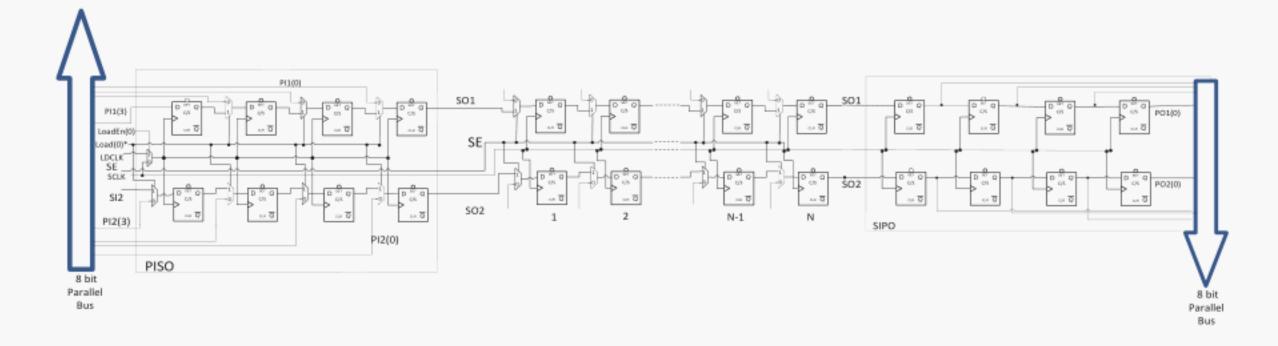

| Figure 47—Four-bit PISO/SIPO on 2 scan channels                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 70                                                                         |

| Figure 48—Use of ERROR_CHAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 73                                                                         |

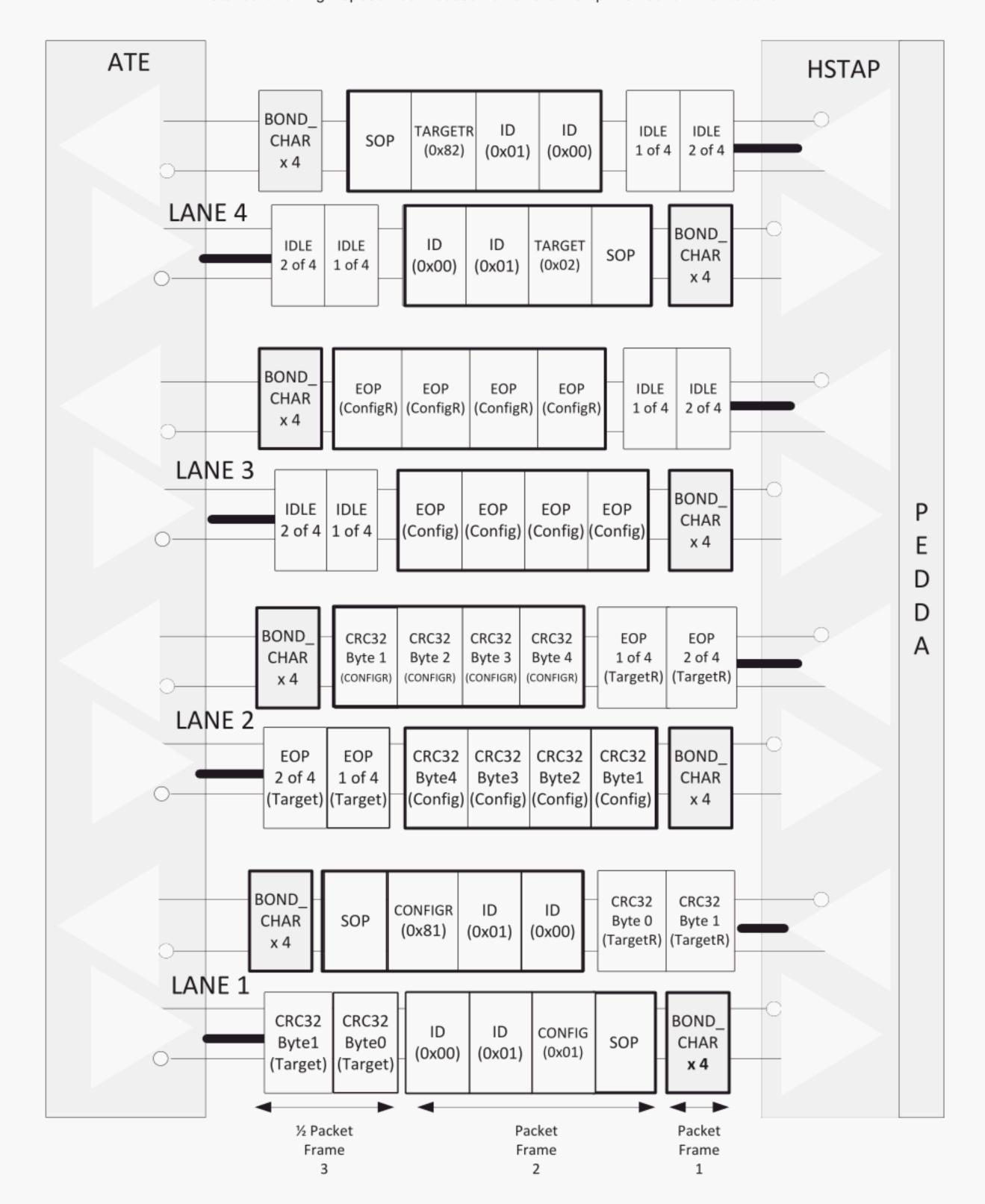

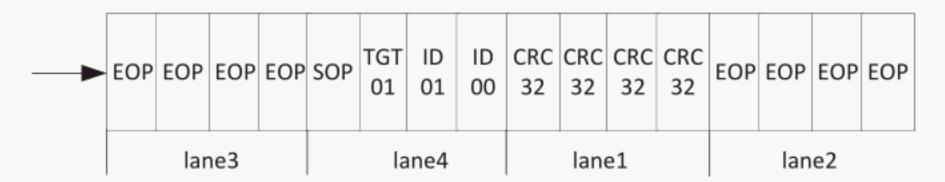

| Figure 49—Four lane HSTAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 79                                                                         |

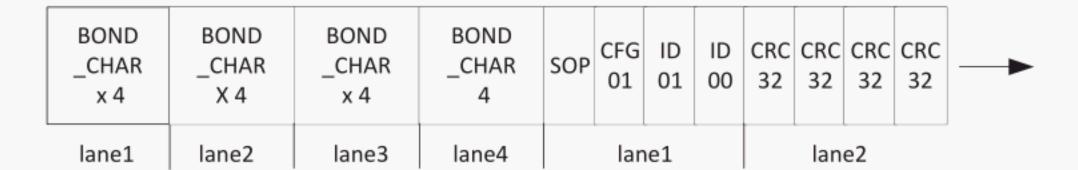

| Figure 50—Striping of data alternative view                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                              |

| Link of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                              |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                              |

| Table 1—Inbound packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |

| Table 1—Inbound packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 28                                                                         |

| Table 1—Inbound packets Table 2—Outbound packets Table 3—CONFIG packet transmit order                                                                                                                                                                                                                                                                                                                                                                                                                  | . 28<br>. 31                                                                 |

| Table 1—Inbound packets Table 2—Outbound packets Table 3—CONFIG packet transmit order Table 4—TARGET packet transmit order                                                                                                                                                                                                                                                                                                                                                                             | . 28<br>. 31<br>. 33                                                         |

| Table 1—Inbound packets Table 2—Outbound packets Table 3—CONFIG packet transmit order Table 4—TARGET packet transmit order Table 5—RESET packet data and transmit order                                                                                                                                                                                                                                                                                                                                | . 28<br>. 31<br>. 33<br>. 35                                                 |

| Table 1—Inbound packets Table 2—Outbound packets Table 3—CONFIG packet transmit order Table 4—TARGET packet transmit order Table 5—RESET packet data and transmit order Table 6—The subset of 64B/66B blocks used when encoding IEEE 1149.10 packets                                                                                                                                                                                                                                                   | . 28<br>. 31<br>. 33<br>. 35<br>. 45                                         |

| Table 1—Inbound packets  Table 2—Outbound packets  Table 3—CONFIG packet transmit order  Table 4—TARGET packet transmit order  Table 5—RESET packet data and transmit order  Table 6—The subset of 64B/66B blocks used when encoding IEEE 1149.10 packets  Table 7—Example 64B/66B encoding of IEEE 1149.10 packets                                                                                                                                                                                    | . 28<br>. 31<br>. 33<br>. 35<br>. 45                                         |

| Table 1—Inbound packets  Table 2—Outbound packets  Table 3—CONFIG packet transmit order  Table 4—TARGET packet transmit order  Table 5—RESET packet data and transmit order  Table 6—The subset of 64B/66B blocks used when encoding IEEE 1149.10 packets  Table 7—Example 64B/66B encoding of IEEE 1149.10 packets  Table 8—BSDL syntax from IEEE Std 1149.1                                                                                                                                          | . 28<br>. 31<br>. 33<br>. 35<br>. 45<br>. 46                                 |

| Table 1—Inbound packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 28<br>. 31<br>. 33<br>. 35<br>. 45<br>. 46<br>. 57                         |

| Table 1—Inbound packets  Table 2—Outbound packets  Table 3—CONFIG packet transmit order  Table 4—TARGET packet transmit order  Table 5—RESET packet data and transmit order  Table 6—The subset of 64B/66B blocks used when encoding IEEE 1149.10 packets  Table 7—Example 64B/66B encoding of IEEE 1149.10 packets  Table 8—BSDL syntax from IEEE Std 1149.1  Table 9—BSDL syntax for IEEE 1149.10 without IEEE Std 1149.1 compliance  Table 10—HSTAP BSDL parameters                                 | . 28<br>. 31<br>. 33<br>. 35<br>. 45<br>. 46<br>. 57<br>. 58                 |

| Table 1—Inbound packets  Table 2—Outbound packets  Table 3—CONFIG packet transmit order  Table 4—TARGET packet transmit order  Table 5—RESET packet data and transmit order  Table 6—The subset of 64B/66B blocks used when encoding IEEE 1149.10 packets  Table 7—Example 64B/66B encoding of IEEE 1149.10 packets  Table 8—BSDL syntax from IEEE Std 1149.1  Table 9—BSDL syntax for IEEE 1149.10 without IEEE Std 1149.1 compliance  Table 10—HSTAP BSDL parameters  Table 11—Packet Map parameters | . 28<br>. 31<br>. 33<br>. 35<br>. 45<br>. 46<br>. 57<br>. 58<br>. 60         |

| Table 1—Inbound packets  Table 2—Outbound packets  Table 3—CONFIG packet transmit order  Table 4—TARGET packet transmit order  Table 5—RESET packet data and transmit order  Table 6—The subset of 64B/66B blocks used when encoding IEEE 1149.10 packets  Table 7—Example 64B/66B encoding of IEEE 1149.10 packets  Table 8—BSDL syntax from IEEE Std 1149.1  Table 9—BSDL syntax for IEEE 1149.10 without IEEE Std 1149.1 compliance  Table 10—HSTAP BSDL parameters                                 | . 28<br>. 31<br>. 33<br>. 35<br>. 45<br>. 46<br>. 57<br>. 58<br>. 60<br>. 68 |

## IEEE Standard for High-Speed Test Access Port and On-Chip Distribution Architecture

#### 1. Overview

#### 1.1 Scope

This standard defines a high speed test access port for delivery of test data, a packet format for describing the test payload, and a distribution architecture for converting the test data to/from on-chip test structures.

The standard re-uses existing high speed I/O (HSIO) known in the industry for the high speed test access port (HSTAP). The HSIO connects to an on-chip distribution architecture through a common interface. The scope includes the distribution architecture test logic and packet decoder logic. The objective of the distribution architecture and packet decoder is that it can be readily re-used with different integrated circuits (ICs) that host different HSIO technology, such that the standard addresses as large a part of the industry as possible.

The scope includes IEEE 1149.1 Boundary-Scan Description Language (BSDL) and Procedural Description Language (PDL) documentation, which can be used for configuring a mission mode HSIO to a test mode compatible with the HSTAP. The same BSDL and PDL can then be used to deliver high-speed data to the on-chip test structures.

#### 1.2 Need

Test time has always been an important metric for system on a chip (SoC). The original IEEE 1149.1 test access port is fine for simple board interconnect tests, but as on-chip operations via the IEEE 1149.1 test access port (TAP) have increased, the use of the IEEE 1149.1 TAP becomes inefficient for board test and on-board field programmable gate array (FPGA) configuration. Large FPGAs take tens of minutes to configure through the IEEE 1149.1 TAP. The IEEE 1149.1 TAP has always been too slow for production SoC test. Wide test access mechanisms (TAMs) are used to increase test throughput during production IC test at the cost of requiring more tester resources. Wide TAMs are also not useful for test re-use at the board/system level because many of the I/O of the TAM are not accessible. Pin limitations also exist where the pins required for the IEEE 1149.1 TAP cannot be supported by a small package or die. A high-speed test access port and packet encoder/decoder and distribution architecture (PEDDA) is needed by the industry to standardize a faster test data delivery mechanism for IC automatic test equipment (ATE), but also be re-usable at board and system level test. Today, in 2017, to get 10 Gbit/s data transfer on a die

requires one hundred touch-downs for sending data in at 100 Mbit/s and one hundred touch-downs for receiving data at 100 Mbit/s with one hundred scan chains that meet the timing for a 100 MHz clock rate. IEEE Std 1149.10-2017™ offers an alternative to deliver the same test data bandwidth with just a differential receiver and transmitter: four pins, a system clock, and power. By making the scan-channels "virtual," tradeoffs can be made during design for test regarding scan rates, number of concurrent active scan channels, and the amount of test bandwidth desired.

Mission mode pins exist for SERDES, serial parallel interface (SPI), I<sup>2</sup>C (I2C), and double data rate (DDR), which can be re-allocated for test purposes saving on dedicated test pins needed in the SoC to support IEEE 1149.1. IEEE Std 1149.10-2017 introduces the re-use of mission mode pins to facilitate either high-bandwidth test or low resource based test via two new objects: the HSTAP and the PEDDA. The HSTAP can layer on top of the mission mode pins (e.g., re-use the pins of SERDES, SPI, I2C, etc.) and deliver data to the PEDDA, which can access on-chip scan channels (test data registers and wrapper serial ports) to communicate data for test, debug, or FPGA configuration.

#### 1.3 Document outline

Circuit designs such as those defined by this standard are more easily understood if their specifications are accompanied by general descriptive material that places the details of the various parts of each design in perspective and provides examples of implementation. Clause 1, therefore, contains an overview of this standard to the testing of an electronic circuit, the need, and document conventions. Clause 2 provides a list of normative references and Clause 3 provides definitions, acronyms, and abbreviations. Subsequent clauses of this document contain the specifications for particular features of this standard.

#### 1.4 Specifications

Material titled "Specifications" contain the rules, recommendations, and permissions that define this standard:

- Rules specify the mandatory aspects of this standard. Rules contain the word shall.

- Recommendations indicate preferred practice for designs that seek to conform to this standard.

Recommendations contain the word should.

- Permissions show how optional features may be introduced into a design that seeks to conform to this standard. These features will extend the application of the test circuitry defined by this standard. Permissions contain the word may.

#### 1.5 Descriptions

#### **CAUTION**

The descriptive material contained in this standard is for illustrative purposes only and does not define a preferred implementation. Examples are provided throughout this standard to illustrate possible circuit implementations. Where discrepancies between examples and specifications may occur, the specifications always take precedence. Readers should exercise caution when using these examples in their specific applications. In particular, it is emphasized that the examples are designed to communicate effectively the meaning of this standard. As such, they are logically correct; however, as always, a particular implementation may not operate properly with respect to timing and other parametric characteristics.

Material not contained in "Specifications" is descriptive material that illustrates the need for the features being specified or their application. This material includes schematics that illustrate a possible implementation of the specifications in this standard. The descriptive material also discusses design decisions made during the development of this standard.

#### 1.6 Text conventions

The following conventions are used in this standard:

a) The rules, recommendations, and permissions in "Specifications" are contained in a single alphabetically indexed list. References to each rule, recommendation, or permission are shown in the form:

- b) Instruction and state names defined in this standard are shown in italic type in the text.

- c) Names of states and signals that control the test data registers defined by this standard contain the characters DR, while those that control the instruction register contain the characters IR.

- d) Names for signals that are active in their low state have an asterisk as the final character, e.g., TRST\*.

- e) A positive logic convention is used; i.e., a logic 1 signal is conveyed as the more positive of the two voltages used for logic signals.

#### 1.7 Logic diagram conventions

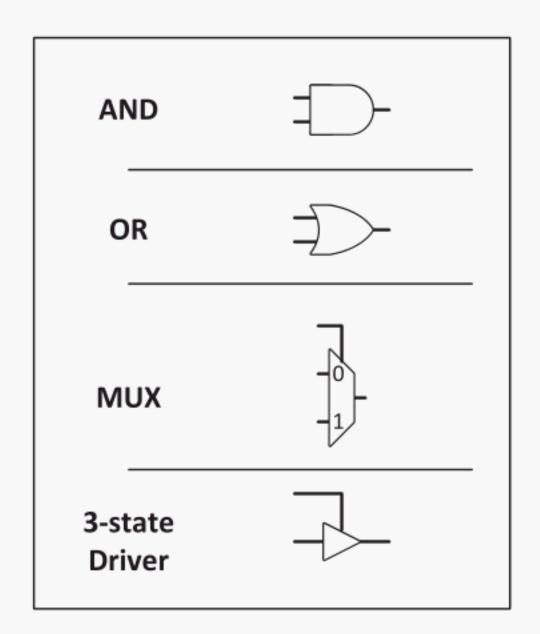

During the different iterations of this standard, logic diagram figures have been added in various styles with differing logic symbols. Figure 1 shows the symbologies currently used for the common combinational logic elements. Symbols for storage elements (generally edge-sensitive flip-flops) are reasonably consistent, although pin names on the element may vary from figure to figure.

Figure 1—Logic symbology used in this standard

#### 2. Normative references

The following referenced documents are indispensable for the application of this document (i.e., they must be understood and used, so each referenced document is cited in text and its relationship to this document is explained). For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments or corrigenda) applies.

IEEE Std 802.3TM, IEEE Standard for Ethernet.1,2

IEEE Std 1149.1™, IEEE Standard for Test Access Port and Boundary-Scan Architecture.

#### 3. Definitions, abbreviations, acronyms, and special terms

#### 3.1 Definitions

For the purposes of this document, the following terms and definitions apply. The *IEEE Standards Dictionary Online* should be consulted for terms not defined in this clause.<sup>3</sup>

channel: A scan-channel.

channel bonding: The use of multiple HSTAPs that work together in order to increase bandwidth.

<sup>&</sup>lt;sup>1</sup> The IEEE standards or products referred to in Clause 2 are trademarks owned by the Institute of Electrical and Electronics Engineers, Incorporated.

<sup>&</sup>lt;sup>2</sup> IEEE publications are available from the Institute of Electrical and Electronics Engineers (http://standards.ieee.org/).

<sup>&</sup>lt;sup>3</sup>IEEE Standards Dictionary Online is available at: <a href="http://dictionary.ieee.org">http://dictionary.ieee.org</a>

**control character**: Any of the special symbols used in serial communication encodings. 8B/10B, for instance, defines twelve control symbols. All of the control characters in this standard are shown and defined as unencoded hexadecimal values of eight bits in width.

CRC32: Cyclical Redundancy Check. All references to CRC32 in this document refer to the 32-bit computation as documented in IEEE Std 802.3.4

**Enable\_1149\_10**: A signal that is an input to the PEDDA when at least one scan-channel is shared with an IEEE 1149.1 TAP. When it is asserted, the PEDDA provides access to one or more scan-channels from a HSTAP. When it is de-asserted, the PEDDA provides access to one or more scan-channels from the IEEE 1149.1 TAP. An IEEE 1149.1 PDL iProc with the same name documents one method to assert the signal, other methods are left to the designer.

**high-speed test access port (HSTAP)**: The HSTAP is the input/output pins and circuitry that deliver data to a PEDDA. It is the test access port of this standard and is not a high-speed version of the IEEE 1149.1 TAP. The HSTAP may include common serial encoding/decoding methods such as 8B/10B, 128B/130B, or others.

**IEEE 1149.10 interface**: A high-speed test access port (HSTAP) and packet encoder/decoder and distribution architecture (PEDDA).

**instruction register**: Refers to the IEEE 1149.1 instruction register. Bit "I" of the ICSU defined section in the scan packet indicates if there is an operation from a HSTAP and PEDDA to an IEEE 1149.1 instruction register. All other "instruction" registers, such as the IEEE 1500 wrapper instruction register, are treated as IEEE 1149.1 test data registers.

**lane**: A serial data transmission path with one transmit and receive pair. The terminology commonly is used with differential signaling, however, for this standard, a single-ended transmit and receive pair also make up a lane. A HSTAP may have one or more lanes.

multi-lane: A mode of operation where multiple lanes are used.

pack: A verb "to place" all the bits for enabled scan-channels contiguous with other enabled scan-channels.

packet frame: A four-byte portion of a packet that starts at any integer multiple of four bytes.

**port**: As used in the acronym, HSTAP, port refers to an input/output interface (e.g., Ethernet port). Port does not mean pin as it would in an IEEE 1149.1 context.

**scan-channel**: Any serially clocked input or output (or both) to or from the PEDDA. A scan-channel may be a scan chain or it may feed the input to a de-compressor, which then fans out to multiple scan chains. A scan-channel may be clocked by a scan clock or the IEEE 1149.1 TCK.

**striping**: The round-robin assignment of packet frames across a given set of HSTAPs during channel-bonding. One packet frame of a given packet is transmitted and received at each HSTAP sequentially.

**TAP interface**: The interface on the PEDDA that accepts the signals from an IEEE 1149.1 TAP. The TAP interface allows IEEE 1149.1 TDRs and IEEE 1500 wrapper serial ports to have shared access between the IEEE 1149.1 TAP and an IEEE 1149.10 HSTAP.

<sup>&</sup>lt;sup>4</sup> Information on references can be found in Clause 2.

#### 3.2 Abbreviations and acronyms

ASIC application-specific integrated circuit

ATE automatic test equipment

ATPG automatic test-pattern generation

BIST built-in self-test

BNF Backus-Naur form

BSDL Boundary-Scan Description Language

CMOS complementary metal-oxide semiconductor

DC direct current

DDR double data rate

ECID electronic chip identification

FIFO first in, first out

HSTAP high speed test access port

I2C I<sup>2</sup>C

IC integrated circuit

ICSU instruction, capture, shift and update

I/O input or output

IP intellectual property (commonly used to refer to a reusable design element)

LSB least significant bit

LVDS low-voltage differential signaling

MSB most significant bit

PDL Procedural Description Language or a file containing PDL statements

PEDDA packet encoder/decoder and distribution architecture

PISO parallel in, serial out

PLL phase-locked loop

POR power-on reset

PRBS pseudo-random binary sequence

RAM random access memory

SERDES serializer/deserializer

SIPO serial in, parallel out

SOC system-on-a-chip

SPI serial parallel interface

TAP test access port

TCK test clock input

Tcl Tool Command Language or a file containing Tcl statements

TDI test data input

TDO test data output

TDR test data register

TMP test mode persistence

TMS test mode select

TRST\* test reset

TTL transistor-transistor logic

UUT unit under test

VHSIC very high-speed integrated circuit

WBR wrapper boundary register

WBY wrapper bypass

WDR wrapper data register

WIR wrapper instruction register

WRSTN wrapper reset

WSC wrapper serial control

WSI wrapper scan in

WSO wrapper scan out

WSP wrapper serial port

#### 3.3 Numbers

Values that are expressed in binary notation will be indicated by a contiguous string of characters starting with 0b or 0B followed by one of the set [01xX], followed by zero or more of the characters in the set [01xX\_], and containing no spaces or format effectors.

Values that are expressed in hexadecimal notation will be indicated by a contiguous string of characters starting with 0x or 0X, followed by one of the set [0-9a-fA-FxX], followed by zero or more of the characters in the set [0-9a-fA-FxX], and containing no spaces or format effectors.

Values expressed in decimal notation shall be an unsigned contiguous string of characters of the set [0-9]; multi-character values shall not start with 0, shall contain no spaces or format effectors, shall have a value less than 232 – 1, and shall always match any binary field large enough to hold the most significant 1 bit of the binary equivalent value of the decimal pattern.

#### 4. High-speed test access port (HSTAP)

#### 4.1 HSTAP

This subclause defines the rules for creating a HSTAP. The HSTAP interfaces between external ATE and the PEDDA.

#### 4.1.1 Description

The HSTAP circuit is the primary interface of the PEDDA. The HSTAP terminology is used to differentiate the IEEE 1149.10 HSTAP from the IEEE 1149.1 TAP that has single-ended signals TCK, TMS, TDI, TDO, and TRST\*. The designer is provided with flexibility in designing the HSTAP as long as the HSTAP can be documented with the HSTAP BSDL attribute and all rules in this clause are followed. A HSTAP must be ready to operate after power-on or after compliance is enabled. The HSTAP can take advantage of re-using mission mode interfaces (e.g., SERDES) only when the HSTAP is ready to respond to IEEE 1149.10 packets after compliance is enabled. There are two methods to enable compliance: use the IEEE 1149.10 compliance-enable character, or provide an IEEE 1149.1 TAP interface to configure mission mode signals into the HSTAP for IEEE 1149.10-based testing.

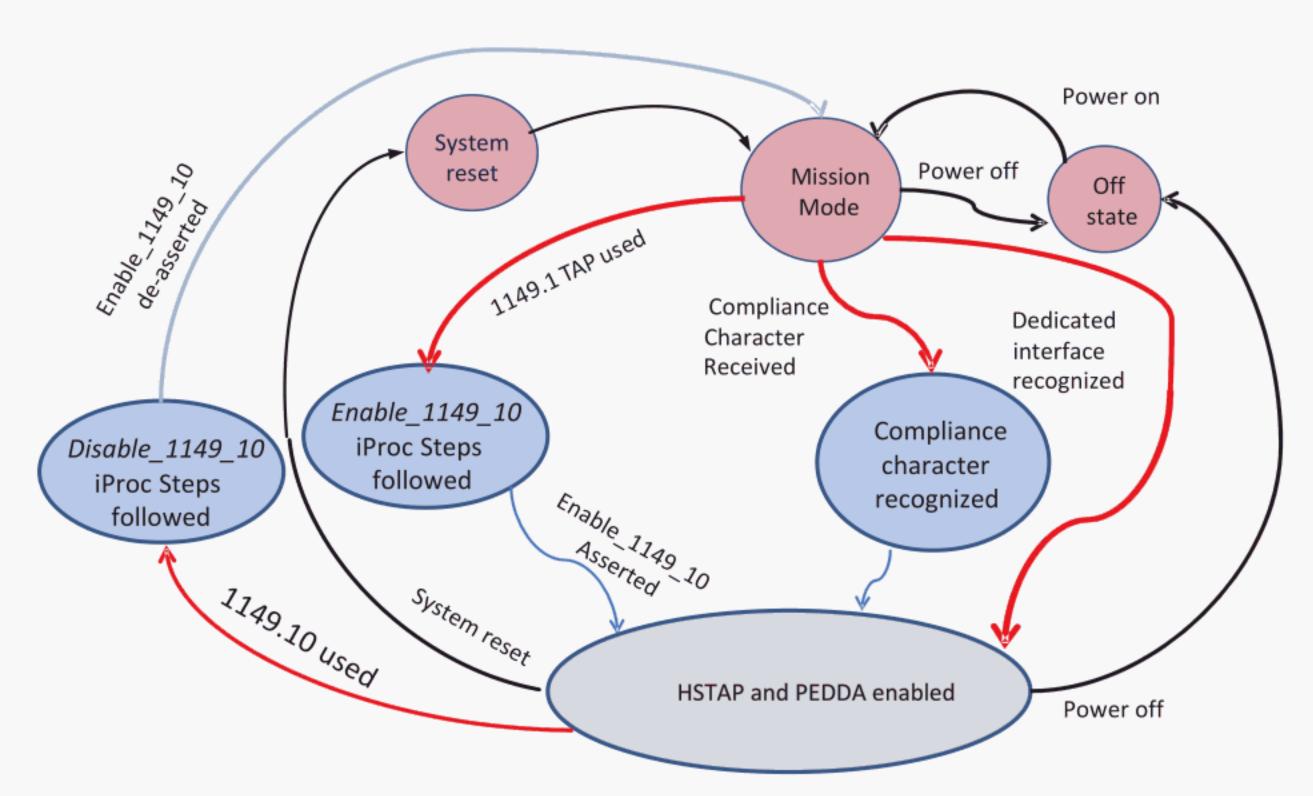

Figure 2—State diagram for IEEE 1149.10 entry

Figure 2 shows the state diagram for enabling the HSTAP and PEDDA. This state diagram illustrates rule 4.1.2 c). After power-on, the device is in mission mode. A HSTAP can be dedicated in its function to support IEEE 1149.10 and not shared with a mission mode function. In that case, the dedicated HSTAP interface is enabled at power-on, as indicated by the path in Figure 2 from the mission mode state directly to the HSTAP and PEDDA enabled state. A dedicated HSTAP and PEDDA are enabled as part of the power-on sequence and do not need compliance enablement. If the HSTAP is shared with a mission mode I/O interface then one of the two compliance enablement methods are needed to enable the HSTAP and PEDDA. A system reset sets the state of a shared HSTAP back to mission mode. The system reset can be performed via system reset pins or through other means such as the IEEE 1149.1 IC\_RESET instruction if it is provided. When an IEEE 1149.1 TAP is provided to enable the HSTAP and PEDDA, a PDL iProc Enable\_1149\_10 must be provided to document the steps to enable compliance. An associated PDL iProc Disable\_1149\_10 can be used by the IEEE 1149.10 interface to set test data register bits to re-enable IEEE 1149.1 TAP operation and mission mode.

#### 4.1.2 Specifications

#### Rules

- a) An IEEE Std 1149.10-2017 compliant design shall have one or more HSTAPs.

- b) Each HSTAP shall be documented using the HSTAP BSDL attribute.

- c) Each HSTAP shall power-up in the enabled state (i.e., ready to respond to a CONFIG packet and all subsequent IEEE 1149.10-defined packets) unless:

- An IEEE 1149.1 TAP interface is designed to enable the IEEE Std 1149.10-2017 compliant operation and the presence of the TAP is documented in BSDL

#### and/or

A compliance-enable character received at the HSTAP interface enables IEEE Std 1149.10-2017 compliance and is documented in the CONTROL\_CHARS BSDL attribute.

- d) If the HSTAP does not power-up in the enabled state, and an IEEE 1149.1 TAP is provided to enable compliance with this standard, two PDL procedures, *Enable\_1149\_10* and *Disable\_1149\_10*, shall be documented.

- e) When compliance is enabled as provided for in rule c) of 4.1.2, the HSTAP shall remain in compliance mode unless

- i. Power to the HSTAP is removed

or

ii. A system reset is performed

or

- iii. The steps documented in the *Disable\_1149\_10* procedure are performed.

- f) If required, the Enable\_1149\_10 PDL procedure shall document the IEEE 1149.1 operations needed such that the HSTAP is ready to respond to a CONFIG packet and all subsequent IEEE 1149.10 defined packets.

- g) A compliance-enable character received at an HSTAP interface shall enable IEEE Std 1149.10-2017 compliance and be forwarded to the HSTAP transmitter to enable connected HSTAPs to enter IEEE Std 1149.10-2017 compliance.

#### Recommendations

h) When an HSTAP is not compliant at power-up, it is recommended that the compliance-enable character be used to establish IEEE Std 1149.10-2017 compliance.

#### 4.1.3 Examples

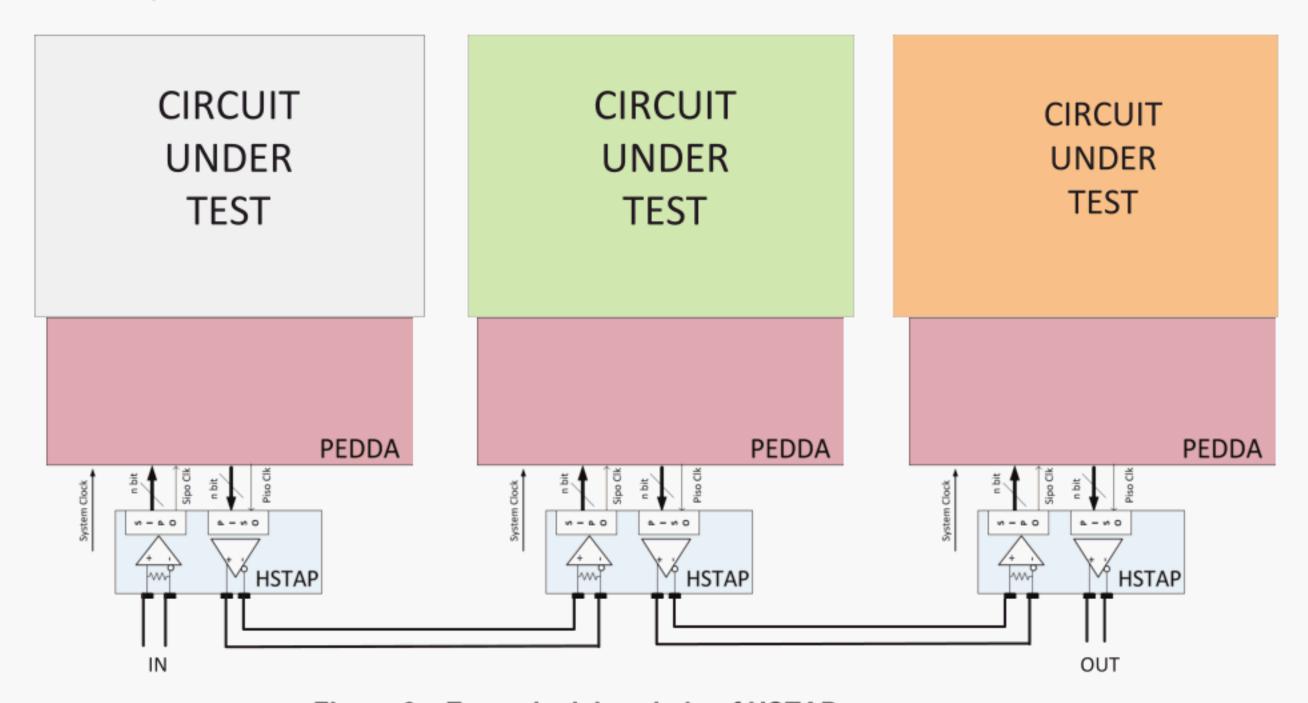

An HSTAP can be daisy-chained to another HSTAP (see Figure 3). The design of the PEDDA and packet format specification enables each HSTAP and PEDDA combination in a daisy-chain to receive data uniquely destined for that PEDDA. (See Clause 5 and Clause 6 for more information on the TARGET\_ID and its use.)

Figure 3—Example daisy chain of HSTAPs

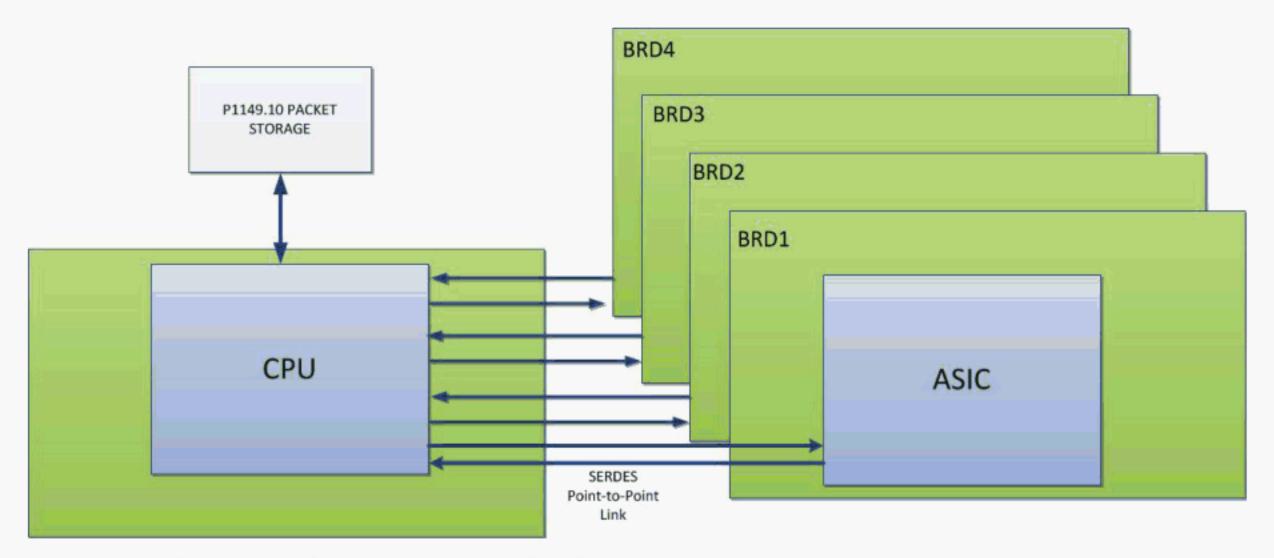

IEEE 1149.10 provides a robust capability for monitoring, measuring, configuring, and testing integrated circuits. The compliance-enable character allows the signals used to be switched from mission mode to IEEE Std 1149.10-2017 compliance. This can be done in-system from a single access point such as a CPU. The other compliance methods require access to the IEEE 1149.1 TAP. This may require physical access outside of the IEEE 1149.10 interface to gain compliance, which may not be achievable. Figure 4 illustrates a system that can benefit from the compliance-enable character. When re-testing of the application-specific integrated circuit (ASIC) in-system is desired, the CPU can send the compliance-enable character over the mission mode point-to-point SERDES links to enable the ASIC to receive IEEE 1149.10 packet information. This provides a capability of in-system test or re-programming of the ASIC over mission mode connections using IEEE 1149.10.

Figure 4—System that benefits from the compliance-enable character

#### 5. Packet encoder/decoder and distribution architecture

#### **5.1 PEDDA**

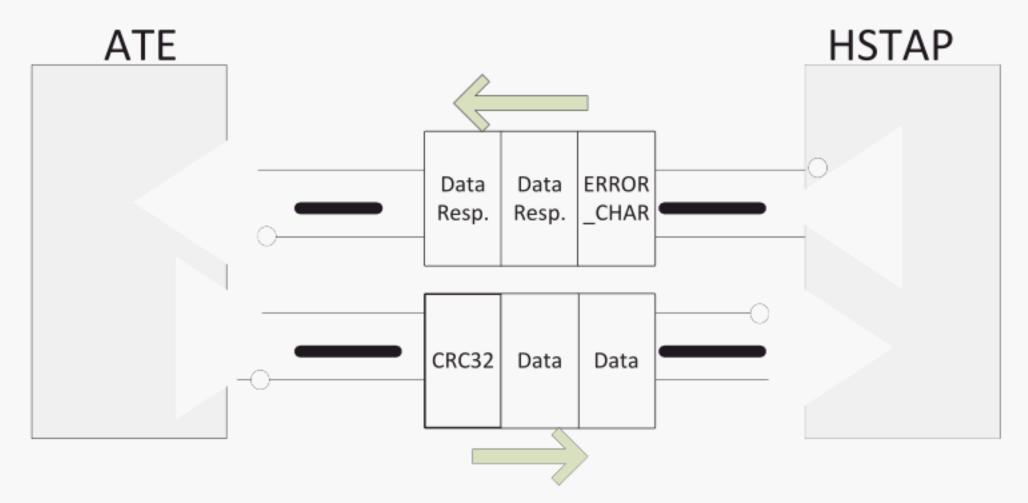

The purpose of the PEDDA is to decode data arriving from the HSTAP and distribute it to the scan channels, while simultaneously collecting responses from the scan channels, encoding the data in packets, and providing them to the HSTAP.

#### 5.1.1 Description

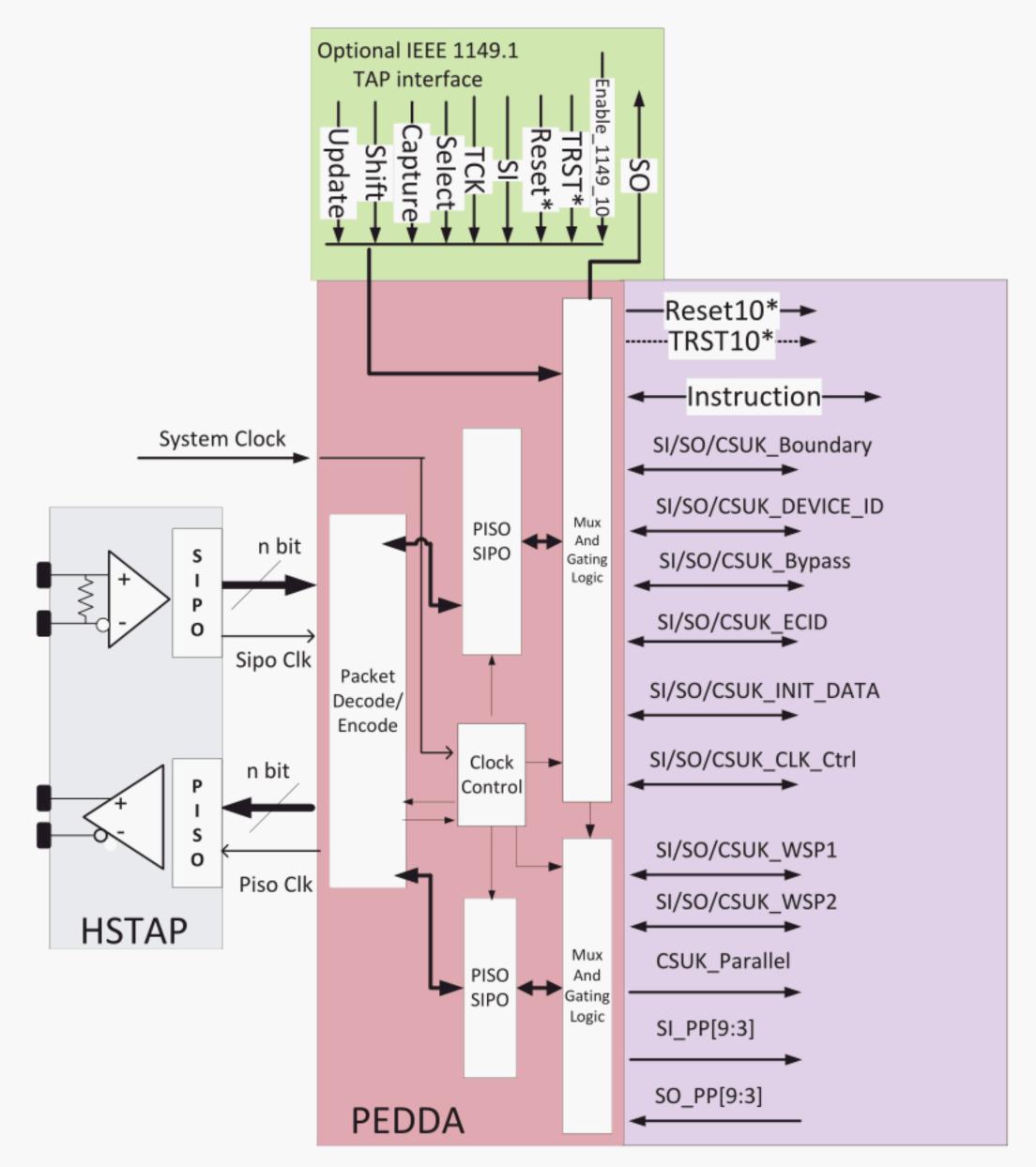

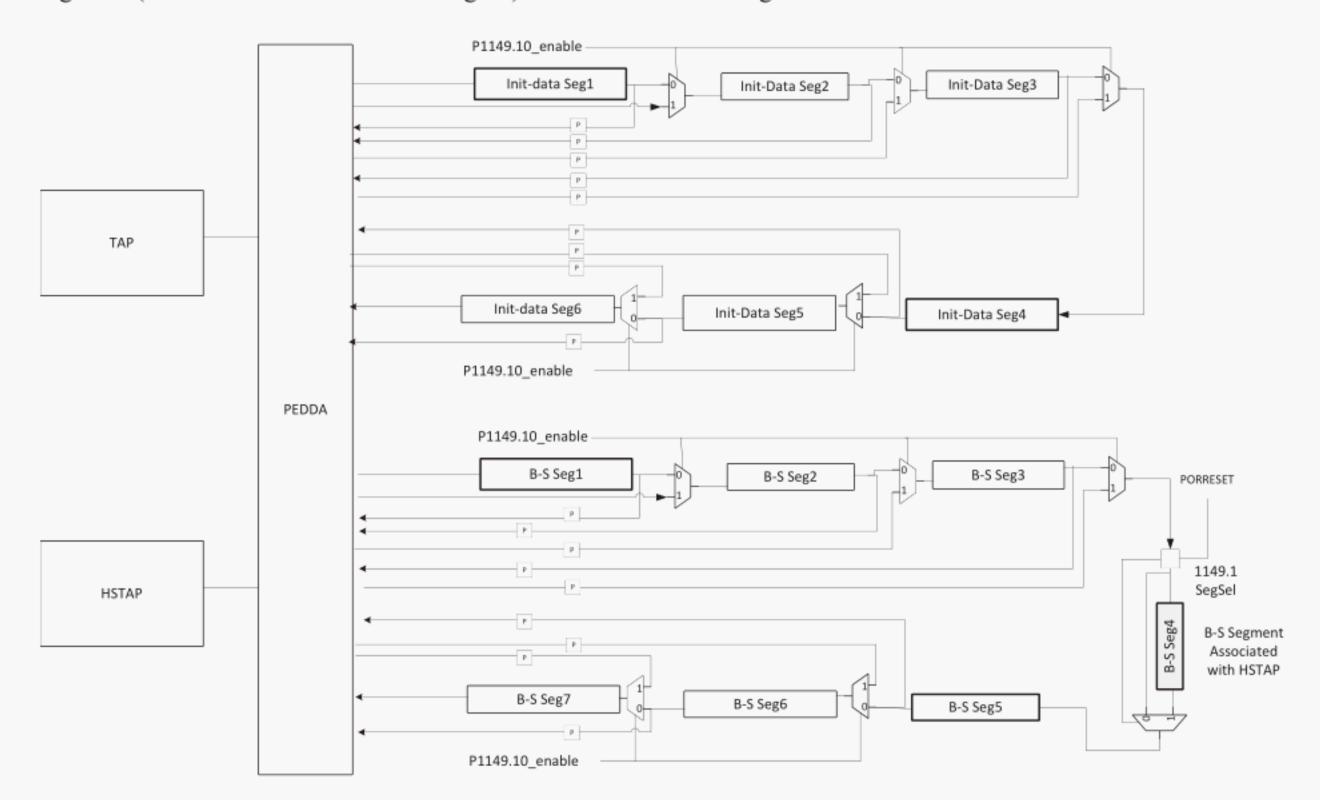

The PEDDA includes three interfaces: an HSTAP interface, a scan-channel interface, and an optional IEEE 1149.1 TAP Inferface. An example block diagram is shown in Figure 5.

Figure 5—Example IEEE 1149.10 PEDDA block diagram

Note in the example that the scan-channel interface includes IEEE 1149.1-accessible registers, IEEE 1500 wrapper serial ports, and a set of parallel scan IEEE 1500 registers. CSUK is an acronym for Capture, Shift, Update, and Clock, the signals that typically control IEEE 1149.1 and IEEE 1500 registers.

When a PEDDA design includes an IEEE 1149.1 TAP interface, it includes inputs from the TAP and one output. SO is scan output, the output of the PEDDA that returns to the TAP. SI is the scan input, which delivers data from the TAP to the TDRs interfaced to the PEDDA. The TCK is the test clock signal defined in IEEE 1149.1. Reset\* is asserted when the IEEE 1149.1 TAP is in the Test-Logic-Reset state as defined in IEEE 1149.1. IEEE Std 1149.1 also defines CH-Reset\*, which is a gated version of Reset\* and cannot be asserted when the TMP Controller is in the Persistence\_on state. When the Enable\_1149\_10 signal is deasserted, the Reset10\* signal is asserted when the TAP interface Reset\* signal is asserted. Reset10\* is distributed in the IC the same way as Reset\* or CH-Reset\* would be in an IEEE 1149.1-only design.

Two methods of interfacing to the PEDDA from an IEEE 1149.1 TAP are allowed. One method uses the *Select*, *Capture*, *Shift*, and *Update* outputs of Figure 6.5 in IEEE Std 1149.1-2013; the other method allows for pre-designed legacy TAPs, which may have separate instruction and data register operation signals.

In rule b) v. of 5.1.2, the *Select* is an output of the TAP controller that determines which way the instruction or data register mux should be set. The signal *Capture* is defined as the logical OR of the Capture\_DR state and the Capture\_IR state. The signal *Shift* is the logical OR of the Shift\_DR and the Shift\_IR state. The signal *Update* is the logical OR of the Update\_DR state and the Update\_IR state. In rule b) vi. of 5.1.2, the signals represent the states Capture\_DR, Shift\_DR, Update\_DR, Capture\_IR, Shift\_IR, and Update\_IR.

#### 5.1.2 Specifications

#### Rules

- a) The PEDDA shall contain at least one HSTAP (see Clause 4) interface and a scan-channel interface.

- b) When this standard's rules require an IEEE 1149.1 TAP [see rule 4.1.2 c)], the PEDDA shall include a TAP interface with the following inputs:

- i. TCK

- ii. SI

- iii. Reset\*

- iv. Enable 1149 10

and either

v. Select, Capture, Shift and Update

or

vi. Capture\_DR, Shift\_DR, Update\_DR, Capture\_IR, Shift\_IR, and Update\_IR and the following output:

vii. SO

When an IEEE 1149.1 TAP is connected to the TAP interface and the Enable\_1149\_10 signal is de-asserted, the PEDDA shall not interfere with the operation and access via the TAP of IEEE 1149.1 test data registers and IEEE 1500 wrapper serial ports connected at the scan-channel interface.

NOTE—When compliance to IEEE 1149.10 is not enabled, then the IEEE 1149.10 circuitry should not interfere with the operation of the scan-channels.<sup>5</sup>

- d) When the Enable 1149 10 signal is asserted the following shall occur:

- SCAN packets arriving at the PEDDA HSTAP interface shall be decoded and delivered to the appropriate scan-channel interface(s).

- Scan data from the scan-channel interface(s) shall be encoded within a SCANR packet and delivered to the HSTAP interface.

- iii. All other IEEE 1149.10 packets shall be decoded and operated on as defined in this standard (see Clause 6) and a corresponding response packet shall be returned to the HSTAP interface.

- All CONTROL\_CHARS shall be operated on as defined in this standard.

- v. When a TAP is connected to the TAP interface and when the TAP is in the Run-Test-Idle or Test-Logic-Reset state, the circuitry of the TAP shall not interfere with the operation of the PEDDA on IEEE 1149.1 test data registers or IEEE 1500 wrapper serial ports connected at the scan-channel interface.

- e) The scan-channel interface shall contain a Reset10\* output.

- f) When a RESET packet is received and the TYPE field bit position RESET10 is a logic one,

<sup>&</sup>lt;sup>5</sup> Notes in text, tables, and figures are given for information only and do not contain requirements needed to implement the standard.

#### IEEE Standard for High-Speed Test Access Port and On-Chip Distribution Architecture

The scan-channel interface shall assert Reset10\* for a period of time determined by the designer and then de-assert it.

and

The de-assert shall occur prior to any capture, shift, or update event which occurs due to the receipt of a SCAN packet.

NOTE—The length of time here cannot be unreasonable. It is possible for the transmitter to send a RESET packet immediately followed by a SCAN packet without IDLE states in between.

- g) When a RESET packet is received and the TYPE field bit position TRST10 is a logic one, and the optional TRST10\* output is provided [see permission 5.1.2 y)], the scan-channel interface shall assert the signal TRST10\*.

- h) When a RESET packet is received and the TYPE field bit position TRST10 is a logic zero, the scan-channel interface shall de-assert TRST10\*.

NOTE—Asserting the signal Reset10\* or the signal TRST10\* does not change HSTAP compliance. See rule 4.1.2 e). This implies that scan registers documented in the PDL iProc *Disable\_1149\_10* must be initialized to mission mode operation using POR or other initialization method.

- i) The PEDDA shall include a 16-bit TARGET\_ID register.

- j) The PEDDA shall be designed such that at power-on-reset or when IEEE 1149.10 compliance is enabled, the PEDDA's TARGET ID register contents shall be set to all zeros.

- k) The PEDDA shall be designed such that when the PEDDA'S TARGET\_ID is all zeros, all packets received except the CONFIG packet are forwarded for transmission.

- The PEDDA shall be designed such that a received CONFIG packet shall change the TARGET\_ID register to the value specified by the <TARGET\_ID> of the CONFIG packet, if the current TARGET\_ID is un-configured (all zeros).

- m) The TARGET\_ID register shall retain its contents unless one of the following occurs:

- The PEDDA circuit is powered-off.

- ii. A RESET packet is received with the TYPE field TARGET\_ID bit is a logic one.

- iii. IEEE 1149.10 compliance is disabled via the TAP.

- n) When a RESET packet is received and the TYPE field bit position TARGET\_ID is a logic one, the scan-channel interface shall set the TARGET\_ID register to all zeros.

- o) The PEDDA shall be designed such that a received TARGET packet that has a TARGET\_ID that matches the TARGET\_ID of the PEDDA, all subsequent packets received until the next TARGET packet received shall be operated on by the PEDDA.

- p) The PEDDA shall be designed such that when a TARGET packet is received that has a TARGET\_ID that does not match the TARGET\_ID of the PEDDA, all subsequent packets until the next TARGET packet received shall be forwarded for transmission.

- q) The PEDDA shall be designed such that a received CONFIG packet with an incorrect CRC32 shall have no effect on the TARGET\_ID register.

- r) The PEDDA shall be designed such that a received TARGET packet with an incorrect CRC32 shall have no effect on the operation of the PEDDA other than to return an ERROR CHAR.

- s) The PEDDA shall be designed such that a received RAW packet with an incorrect CRC32 shall have no effect on the operation of the PEDDA other than to return an ERROR\_CHAR.

- The PEDDA shall be designed such that if it has access to an IEEE 1149.1 boundary-scan register, said boundary-scan register shall have boundary-scan cells associated with the HSTAP signals on an excludable segment.

NOTE—If IEEE 1149.10 is used to take a device into EXTEST, EXTEST\_PULSE, EXTEST\_TRAIN, SELECTIVE\_TOGGLE, the boundary-scan register needs to be segmented at the HSTAP such that the HSTAP signals remain in mission-mode. See IEEE Std 1149.1 for details on excludable segments. See Figure 9.

#### Recommendations

- u) The Reset10\* signal should be routed to registers according to IEEE 1149.1 rules for RESET\* when the PEDDA scan-channel interface is connected to IEEE 1149.1 test data registers.

- v) The TRST10\* signal, when provided, should be routed to registers according to IEEE 1149.1 rules for TRST\* when the PEDDA scan-channel interface is connected to IEEE 1149.1 test data registers.

- NOTE—These two recommendations are necessary to follow when an associated IEEE 1149.1 TAP is present and IEEE 1149.1 compliance is desired in addition to IEEE 1149.10. These signals should not be connected to registers which set or initialize IEEE 1149.10 compliance. See rule 4.1.2 e).

- w) The Reset10\* signal should be routed to registers according to IEEE Std 1500 [B1] rules for WRSTN when the PEDDA scan-channel interface is connected to IEEE 1500 registers.

- NOTE—This recommendation is necessary to maintain IEEE Std 1500 [B1] compliance when IEEE Std 1500 is used for test data registers, and IEEE Std 1500 compliance is desired in addition to IEEE Std 1149.10-2017 compliance.

- x) When it is feasible, a device that can benefit from IEEE Std 1149.1 compliance should be both IEEE Std 1149.1 and IEEE Std 1149.10-2017 compliant.

- NOTE—Be careful not to simply abandon IEEE Std 1149.1 compliance in favor of IEEE Std 1149.10-2017 compliance without giving it some thought. IEEE Std 1149.1 offers a detailed boundary-scan register description that facilitates PCB-level test. System designers and OEMs may still require use of that boundary-scan register and the low speed TAP interface even if IEEE Std 1149.10-2017 is implemented.

#### **Permissions**

- y) When a TAP is connected to the TAP interface, the PEDDA may include a TRST\* input.

- z) A PEDDA may include a scan-channel interface TRST10\* output.

- aa) A PEDDA may include a TAP interface with a connected TAP even when a TAP interface is not required by Rule 4.1.2 c)i.

- NOTE—A TAP can be used with a PEDDA even if the HSTAP does not require a TAP to enter compliance.

#### 5.1.3 Examples

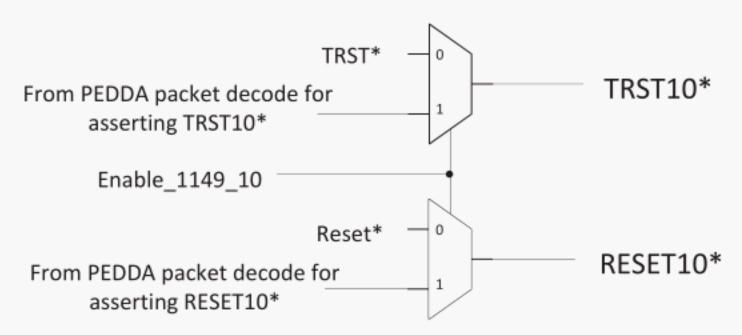

Figure 6 shows an example implementation that meets rules 5.1.2 f), g), and h). If the IEEE 1149.1 TAP is in *Test-Logic-Reset* then there is no effect on Reset10\* or TRST10\* when Enable\_1149\_10 is asserted.

Figure 6—Example implementation of TRST10\* and Reset10\*

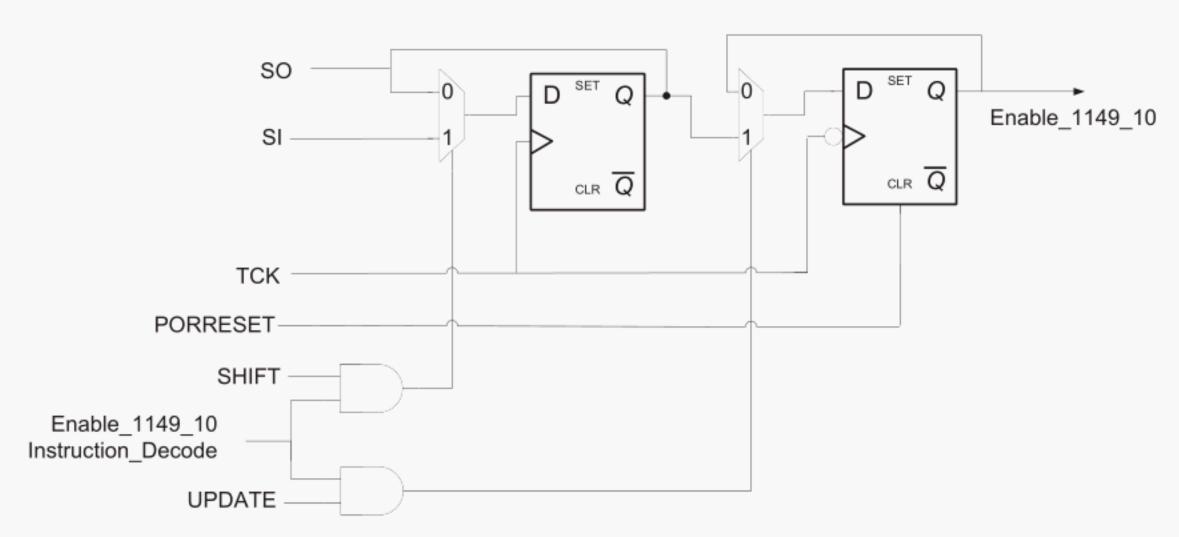

Figure 7 shows an example TDR bit designed to assert Enable\_1149\_10 via the IEEE 1149.1 TAP. PORRESET is an IEEE 1149.1 description of a reset that occurs at power-on (or power-up). At power-on, a reset is performed to clear the update flop to zero and disable IEEE 1149.10 operation. This is just an example; other register bits may need to be set to configure the mission mode signals to operate as an HSTAP. See Clause 9 for more information on how PDL can operate this register.

Figure 7—Example IEEE 1149.1 TDR for asserting Enable\_1149\_10

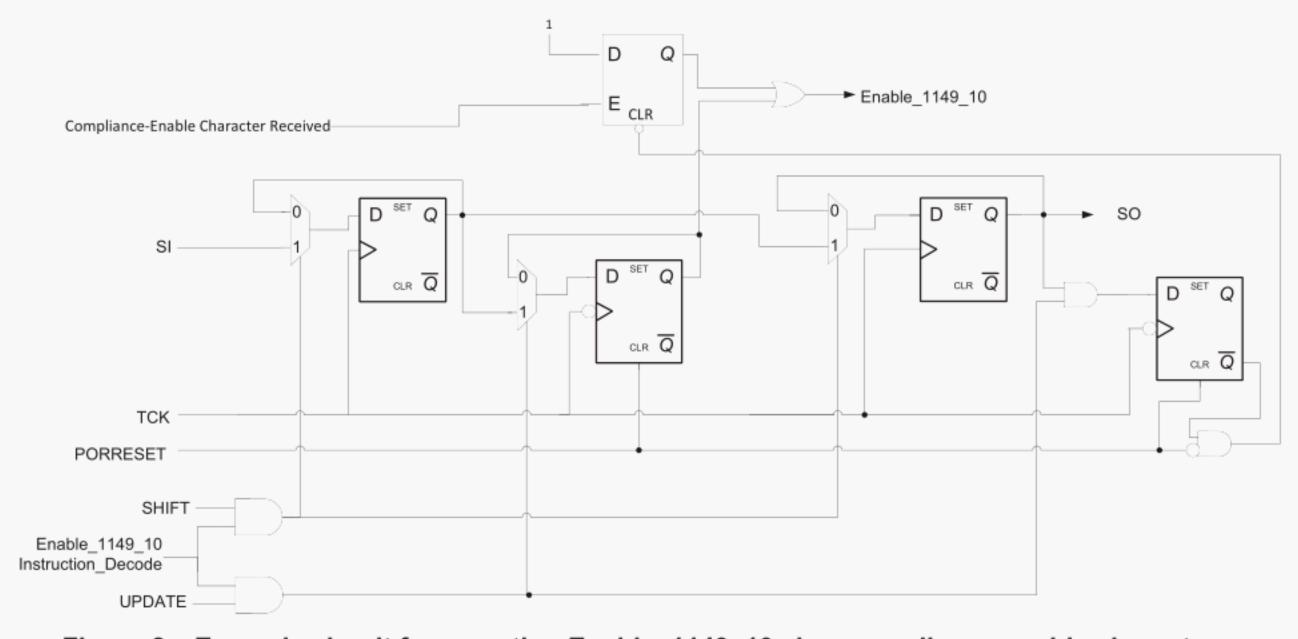

Figure 8 shows an example that uses both the compliance-enable character and an IEEE 1149.1 TDR to assert Enable\_1149\_10. The example shows a circuit that asserts Enable\_1149\_10 when either the compliance-enable character is received or via the IEEE 1149.1 TAP. An IEEE 1149.1 PULSE0 bit is used to de-assert Enable\_1149\_10 such that the rules in rule e) of 4.1.2 are met.

Figure 8—Example circuit for asserting Enable\_1149\_10 via a compliance-enable character

Figure 9 shows an example block diagram of how to segment TDRs for optimal use with IEEE 1149.10, and how to achieve compliance with rule t) of 5.1.2. The figure illustrates shared access via the TAP and HSTAP to the init-data register and the boundary-scan register. The access via the HSTAP is optimized by segmenting the two TDRs into multiple segments that can be scanned concurrently. Concurrent access enables better usage of the bandwidth provided by the HSTAP and shortens test time. The boundary-scan register and the init-data register are used for a variety of pin related tests. Leakage tests, Pull-up/Pull-down, V<sub>OH</sub>/V<sub>OL</sub>, and related pin tests can be tested faster when segmentation is present because the HSTAP/PEDDA can access each segment concurrently. This segmentation can also be used to achieve compliance with rule t) of 5.1.2. Without segmentation, tests using the boundary or init-data register would not be any faster than with an IEEE 1149.1 TAP for access. Figure 9 shows how to put the boundary-scan (b-s) cells associated with the HSTAP on a collapsible segment. This is necessary in order to leave the

HSTAP in mission mode when instructions such as EXTEST, EXTEST\_PULSE, etc. are used; they will not put the HSTAP related b-s cells in test mode. Note that segments can have any number of pipeline registers (shown as the box "P" in the figure) in order to meet timing.

Figure 9—Example use of B-S and Init-Data Register

#### 6. Packet definitions

#### 6.1 Packet overview

This subclause provides the general overview of the inbound and outbound packets defined by this standard.

#### 6.1.1 Description

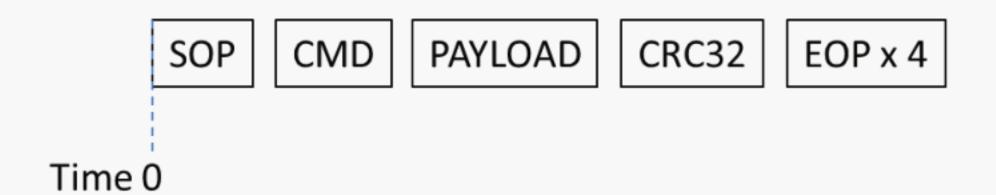

This standard defines two packet types: inbound packets and outbound packets. The IEEE 1149.10 protocol also includes control characters that are used to define the start and end of a packet and any special communications such as error states or idle states. Each packet has a command that controls operation of the PEDDA. Inbound packets are listed in Table 1 and outbound packets are listed in Table 2. The full descriptions are available in the associated packet description in this clause.

Table 1—Inbound packets

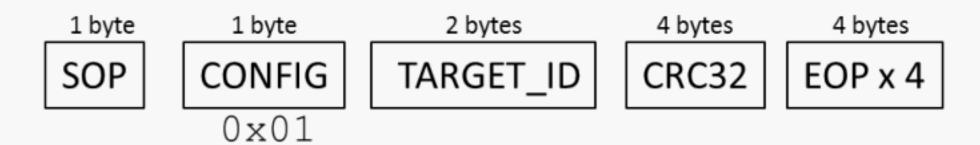

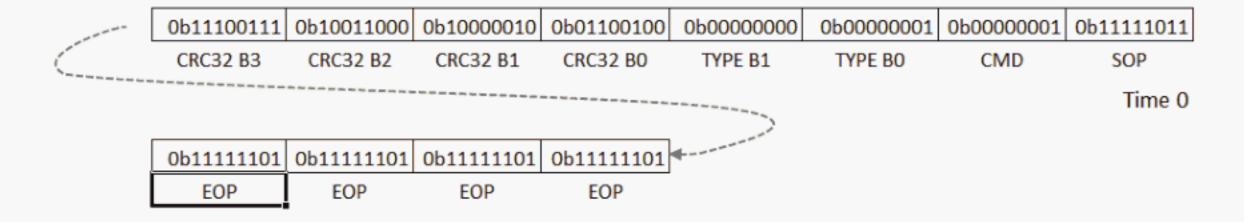

| Command              | Value       | Description                                       |  |

|----------------------|-------------|---------------------------------------------------|--|

| CONFIG               | 0x01        | Enable uninitialized IEEE 1149.10 interface to be |  |

|                      |             | enumerated.                                       |  |

| TARGET               | 0x02        | Specify the target IEEE 1149.10 interface for all |  |

|                      |             | subsequent packets.                               |  |

| RESET                | 0x03        | Assert Reset10* or TRST10* (internally different  |  |

|                      |             | signals) or clear the TARGET_ID.                  |  |

| RAW                  | 0x04        | Enable the interface in a RAW data mode           |  |

|                      |             | (suitable for BER testing). Data is not processed |  |

|                      |             | by the packet processor and subsequently all RX   |  |

|                      |             | data is sent to the TX.                           |  |

| CH-SELECT            | 0x05        | Set the SCAN_GROUP and target channels on         |  |

|                      |             | subsequent IR/DR scan packets.                    |  |

| SCAN                 | 0x06        | An interleaved packet for IR/DR scans.            |  |

| BOND                 | 0x07        | Signal the HSTAP to go from single lane to        |  |

|                      |             | multi-lane.                                       |  |

| USER                 | 0x20-0x3F   | A user-defined packet used to transfer data not   |  |

|                      |             | anticipated by this standard.                     |  |

| All outbound packets | See Table 2 | All response packets are ignored by the input and |  |

|                      |             | forwarded unmodified to the TX.                   |  |

Table 2—Outbound packets

| Command         | Value       | Description                                            |

|-----------------|-------------|--------------------------------------------------------|

| CONFIGR         | 0x81        | A CONFIG packet response.                              |

| TARGETR         | 0x82        | A TARGET packet response.                              |

| RESETR          | 0x83        | A RESET packet response.                               |

| RAWR            | 0x84        | A RAW packet response.                                 |

| CH-SELECTR      | 0x85        | A CH-SELECT packet response.                           |