# package封装

https://zhuanlan.zhihu.com/p/1896206164573782105

https://www.ab-sm.com/a/23456

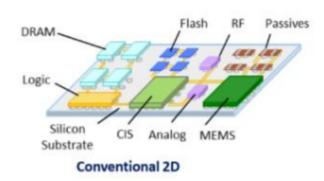

#### 1. 传统2D封装

物理结构:所有芯片和无源器件均安装在基板平面上,芯片和无源器件与XY平面直接接触。

电气连接:通过基板上的布线和过孔实现电气互连,通常使用键合线将芯片与基板连接。

特点:技术成熟,成本较低,但集成度有限,信号传输距离相对较长,可能导致信号延迟。

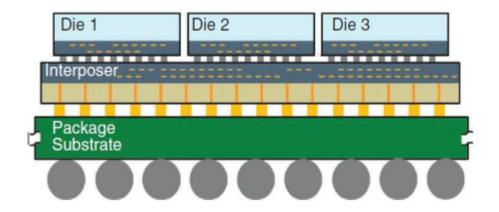

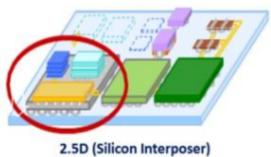

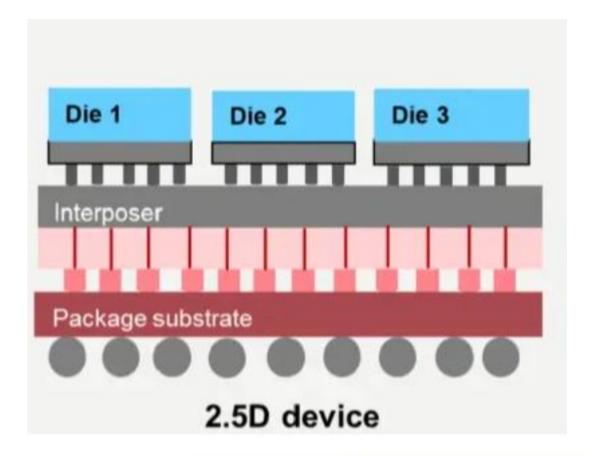

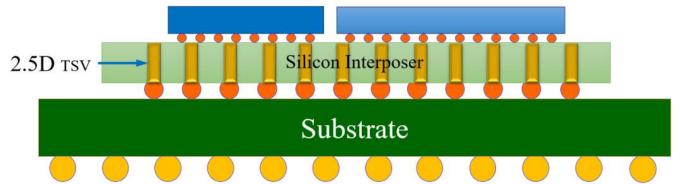

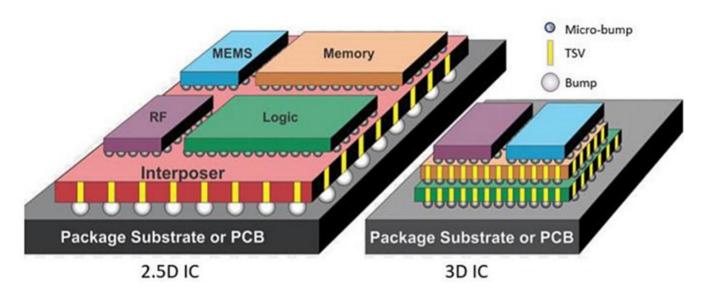

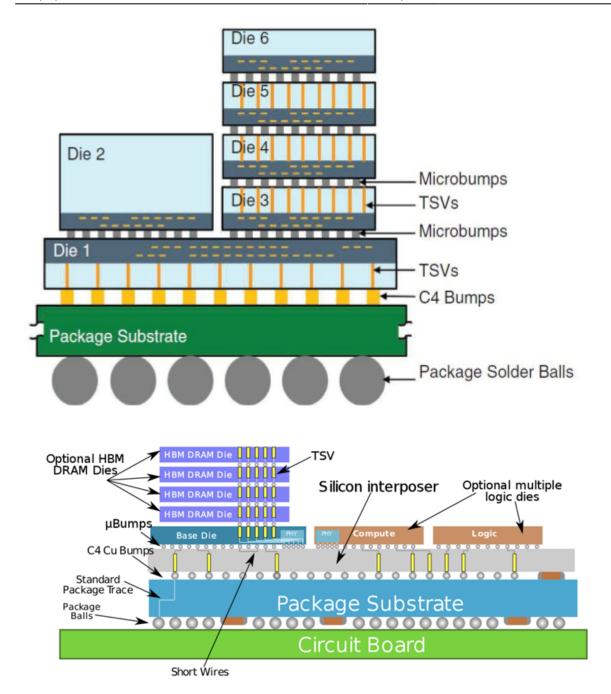

### 2. 2.5D封装

物理结构:芯片堆叠或并排放置在具有TSV的中介层□interposer□上,中介层提供芯片之间的连接性。

电气连接:通过中介层上的微型凸点[micro-bumps[]和TSV实现电气互连。

特点:集成度较高,可以提供更高的I/O密度和更低的传输延迟,但相比3D封装,其垂直堆叠的芯片数量较少。

### 2.5D和3D IC设计

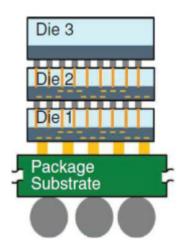

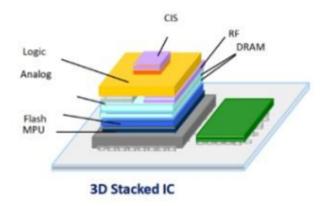

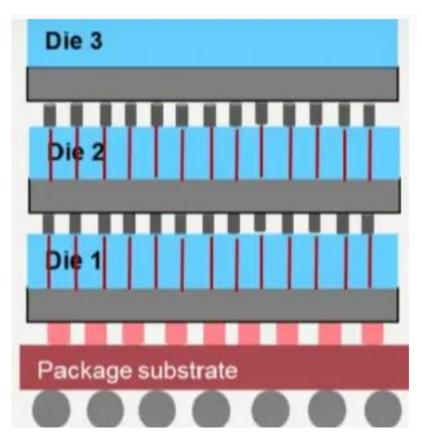

## 3. 3D封装

物理结构:逻辑裸晶或存储裸晶垂直堆叠在一起,通过TSV实现硅芯片之间的垂直互连。

电气连接[TSV技术实现多层硅晶圆与采用TSV的组件之间的连接。

特点:集成度最高,可以实现高密度的垂直互连,提供更高的带宽和更低的功耗,但技术难度和成本也相 对较高。

4. 3.5D封装

#### 5. RDL

RDL□Re-distributed layer□□作为实现芯片水平方向电气延伸和互连的关键技术,在 3D/2.5D 封装集成以及FOWLP□扇出型晶圆级封装)中发挥着举足轻重的作用。它通过在芯片表面沉积金属层和相应的介电层,巧妙地形成金属导线,并将 IO 端口重新设计到更宽敞的区域,构建出表面阵列布局。这一创新技术不仅使得芯片间的键合更薄,简化了工艺,还让设计人员能够以更为紧凑和高效的方式放置芯片,从而显著减少了器件的整体占地面积。

突破传统I/O布局限制传统芯片的I/O端口通常位于边缘,而RDL通过金属布线(如铜导线)将其重新排布为面阵列,支持更密集的引脚布局(如从数百个I/O提升至数千个)。

**提升电气性能** 通过缩短信号传输路径,减少寄生电容和电感,降低延迟(例如在高性能计算芯片中可减少30%以上的路径长度),并优化信号完整性。

支持多芯片集成 在2.5D/3D封装中□RDL连接不同功能的堆叠芯片(如逻辑芯片与存储器),而TSV□硅通孔)负责垂直互连,两者协同实现高带宽集成(如HBM存储器的总线宽度提升至1024位)。

**降低成本与封装尺寸** 通过优化布线设计减少冗余金属层,降低材料成本;同时支持更紧凑的封装形式(如扇出型晶圆级封装FOWLP□使封装面积接近芯片尺寸